# Test-Bus Controller SN74ACT8990

Peter Forstner

Standard Linear & Logic

### **ABSTRACT**

This application report describes IEEE Std 1149.1 test-bus controller (TBC) SN74ACT8990 from Texas Instruments (TI™). The first part explains the architecture and operation of the TBC; the second part uses examples to explain the programming procedure.

#### Contents

| 1 | Introduction                                 | 3  |

|---|----------------------------------------------|----|

| 2 | Hardware                                     | 5  |

|   | 2.1 Processor Interface                      |    |

|   | 2.2 Test Bus Interface                       |    |

|   | 2.3 Architecture                             |    |

|   | 2.3.1 Sequence Block                         |    |

|   | 2.3.2 Serial Block                           |    |

|   | 2.3.3 Event Block                            |    |

|   | 2.3.4 Counter Block                          |    |

|   | 2.3.5 Command Block                          |    |

|   | 2.3.6 Host Block                             |    |

| 3 | Programming                                  |    |

| • | 3.1 Registers                                |    |

|   | 3.2 Typical Programming Procedure            |    |

|   | Examples                                     |    |

| 4 | ·                                            |    |

|   | 4.1 Example Test Board                       |    |

|   | 4.2 Software Examples                        |    |

|   | 4.2.1 Load Commands in Test Board            |    |

|   | 4.2.2 Load Test Vector in Test Board         |    |

|   | 4.2.3 Copy SHIFTER-FIFO Into the Read Buffer |    |

|   | 4.2.4 EXTEST                                 |    |

|   | 4.2.5 PRPG/PSA                               |    |

|   | 4.2.6 Event-Controlled PRPG/PSA              |    |

|   | 4.2.7 Implement PRPG/PSA                     | 73 |

| 5 | Summary                                      | 77 |

# **List of Figures**

| 1  | Test System With TBC SN74ACT8990                                                                   | 3  |

|----|----------------------------------------------------------------------------------------------------|----|

| 2  | System With Built-In Self-Test (BIST)                                                              |    |

| 3  | Connection of the TBC to a Microprocessor                                                          | 5  |

| 4  | Timing Diagram of Processor Interface When Writing                                                 | 6  |

| 5  | Timing Diagram of Processor Interface When Reading                                                 | 6  |

| 6  | Connection of a IEEE Std 1149.1 Test Bus to the TBC                                                | 7  |

| 7  | Connection of Two IEEE Std 1149.1 Test Buses to the TBC                                            | 8  |

| 8  | Connection of Several IEEE Std 1149.1 Test Buses to the TBC, With Buffering of the Test Bus Signal | 9  |

| 9  | Block Diagram of TBC SN74ACT8990                                                                   | 10 |

| 10 | Sequence Block                                                                                     | 11 |

| 11 | Link-Delay Logic                                                                                   | 12 |

| 12 | Serial Block                                                                                       | 13 |

| 13 | Inputs of the Event Block                                                                          | 15 |

| 14 | Outputs of the Event Block                                                                         | 16 |

| 15 | COUNTER20 and COUNTER21 Configured as Separate 16-Bit Counters                                     | 17 |

| 16 | COUNTER20 and COUNTER21 Configured as Combined 16-Bit Counters                                     | 17 |

| 17 | COUNTER20 and COUNTER21 Configured as One 32-Bit Counter (COUNTER2)                                | 18 |

| 18 | Counter Block                                                                                      | 18 |

| 19 | Command Block                                                                                      | 19 |

| 20 | Host Block                                                                                         | 20 |

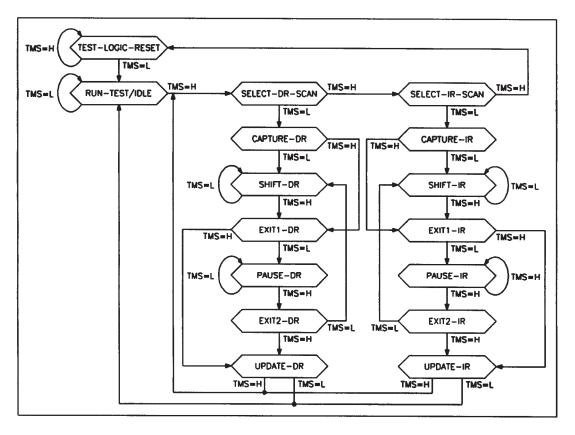

| 21 | IEEE Std 1149.1 Test Access Port (TAP) Status Diagram                                              | 44 |

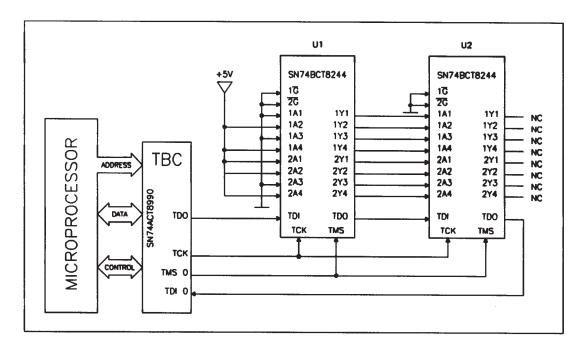

| 22 | Hardware Example: Two SCOPE Octals SN74BCT8244N                                                    | 45 |

### 1 Introduction

There has been a dramatic increase in the complexity of electronic systems as a result of advances in the integration of semiconductors, the introduction of new packaging techniques [surface-mount device (SMD)], and the consequent use of double-sided circuit boards. However, increased component density on circuit boards presents challenges to testability because the number of necessary test vectors increases out of proportion with complexity. By using nail-bed adapters, it is possible to partition the system to be tested, thereby reducing significantly the number of test vectors, although high SMD component density on double-sided boards reduces the number of possible contact areas for nail-bed adapters. Therefore, the escalating problems of testability can be solved only with a completely new concept.

In 1985, leading electronic manufacturers founded the Joint Test Action Group (JTAG) to develop a new and cost-effective test concept. The result of this was IEEE Std 1149.1. This standard requires the use of special test circuits at the inputs and outputs of selected semiconductor components, together with logic to control such test circuits. A 4-wire serial test bus combines the test circuits into a complete test group that is controlled via the test bus. In this way, with only four lines, the complete system can be partitioned and tested.

TI application report EB193 describes these test methods in detail, and presents IEEE Std 1149.1-compatible system controllability observability partitioning environment (SCOPE™) bus drivers from TI. Application report EB203 assumes an understanding of test methods compliant to IEEE Std 1149.1.

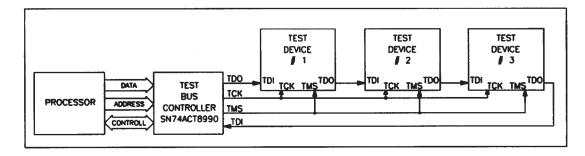

The control of an IEEE Std 1149.1-compatible test system usually is performed by a computer. TBC SN74ACT8990, which can be connected to a computer like a normal interface circuit, completely controls the IEEE Std 1149.1 test bus (see Figure 1). The computer first configures the TBC, then loads in parallel the test commands and test vectors. The TBC transfers these commands and vectors to the system, thereby generating the signal sequence required by IEEE Std 1149.1. The processor can read the result in parallel from the TBC, after the test data has addressed the logic to be tested. This application report describes the operation of the TBC, and explains the programming procedure with examples.

Figure 1. Test System With TBC SN74ACT8990

SCOPE is a trademark of Texas Instruments.

To reduce the applications work by the user needed to control IEEE Std 1149.1-compatible test systems, TI offers the computer program Advanced Support System for Emulation and Test (ASSET™) together with a plug-in computer board. TBC SN74ACT8990 is used on this board. ASSET allows easy development of test programs for which the user needs no understanding of the function of the TBC. First, a library with the IEEE Std 1149.1-compatible circuits that are to be used must be assembled. A library with all standard TI components is supplied. Then, the complete system to be tested must be described with components from the library. After the system description, ASSET needs only the test vectors before testing can begin. This system also is suited ideally to supporting the circuit designer during the test phase.

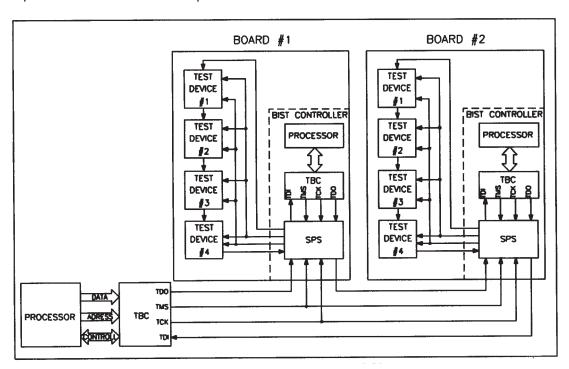

If built-in self-test (BIST) is to be incorporated into an electronic system, TBC SN74ACT8990, in combination with the scan-path selector SN74ACT8999 and a microprocessor, provides an ideal basis (see Figure 2). The main computer can give the microprocessor the signal to start BIST via the IEEE Std 1149.1 test bus. The result of the self-test is communicated from the microprocessor to the main computer.

Figure 2. System With Built-In Self-Test (BIST)

If a large system is composed of several subsystems, it is advantageous to have BIST in each subsystem. The self-test then can be implemented simultaneously in all subsystems, resulting in significant reduction of test time.

This is one of the cases in which direct programming of the TBC is necessary, and in which this application report is intended to give assistance.

ASSET is a trademark of Texas Instruments.

### 2 Hardware

TBC SN74ACT8990 provides the interface between a processor and the IEEE Std 1149.1 test bus. Both interfaces can be operated asynchronously, that is, the clock of the computer does not need to be synchronized with the test clock TCK.

### 2.1 Processor Interface

The processor interface consists of the following:

- 5-bit address bus (A0–A4)

- 16-bit data bus (D0-D15)

- Read line (RD)

- Write line (WR)

- Status line (RDY)

- Interrupt line (INT)

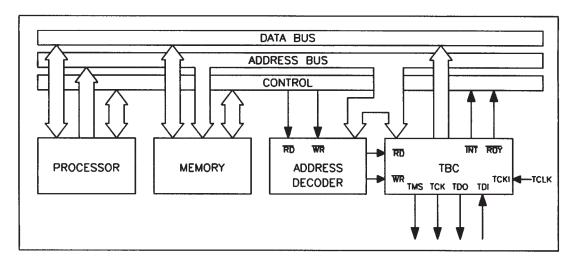

The TBC is connected to the processor like a normal interface circuit, whereby the address decoder can be implemented as PAL (see Figure 3). Clock signal TCLK is buffered in the TBC, then transferred to the test system as the TCK signal, which can be derived from an independent clock generator or the processor clock, or be provided from the test system.

Figure 3. Connection of the TBC to a Microprocessor

Five address lines can be used to address 24 internal registers:

- Ten control registers

- Two command registers

- Six registers to control internal counters

- Four status registers

- One register for transmit data

- One register for receive data

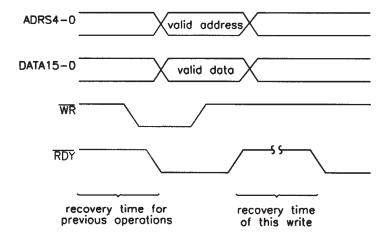

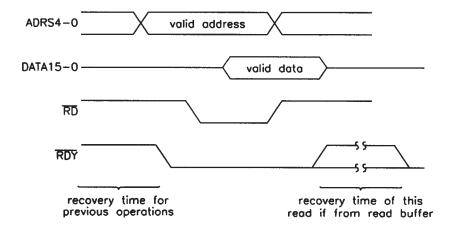

Sixteen registers can be read and overwritten, seven are readable only, and one register can only be written to. The remaining eight potential registers are not occupied. Section 3, Programming, gives details of the registers. The timing of a write cycle is shown in Figure 4, and a read cycle is shown in Figure 5.

Figure 4. Timing Diagram of Processor Interface When Writing

Figure 5. Timing Diagram of Processor Interface When Reading

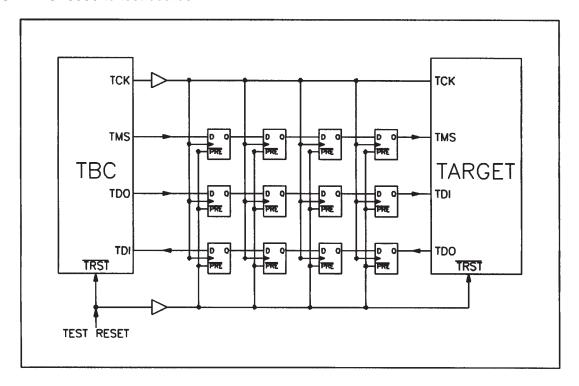

#### 2.2 Test Bus Interface

According to IEEE Std 1149.1, the test bus interface consists of:

- One test pulse input (TCKI)

- One test pulse output (TCKO)

- One test data output (TDO)

- Two test data inputs (TDI0, TDI1)

- Two test mode select outputs (TMS0, TMS1)

- Four lines, which can be used as further TMS outputs (TMS2–TMS5), or can be programmed as event inputs/outputs (EVENT0–EVENT3)

- One line, test bus off (TOFF), to reset all test outputs to a high-resistance state

- One input, test bus reset (TRST), to reset the TBC and all test circuits. The use of this input is optional because the TBC and the test systems have a software reset.

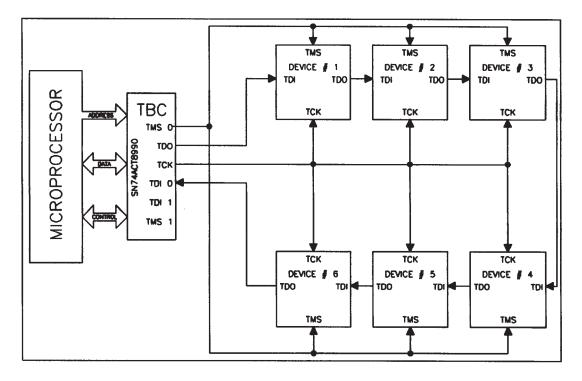

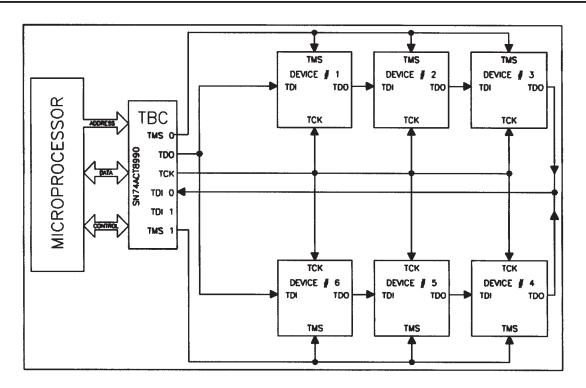

Figure 6 shows the connection of an IEEE Std 1149.1 test system to the TBC. Here, only one TMS signal is needed so that ,in this case, all four event inputs/outputs (EVENT0–EVENT3) are available. Because signals TMS2–TMS5 use the same lines as event inputs/outputs, the number of available event inputs/outputs is reduced if more than two test systems are connected to the TBC (see Figure 7).

Figure 6. Connection of a IEEE Std 1149.1 Test Bus to the TBC

Figure 7. Connection of Two IEEE Std 1149.1 Test Buses to the TBC

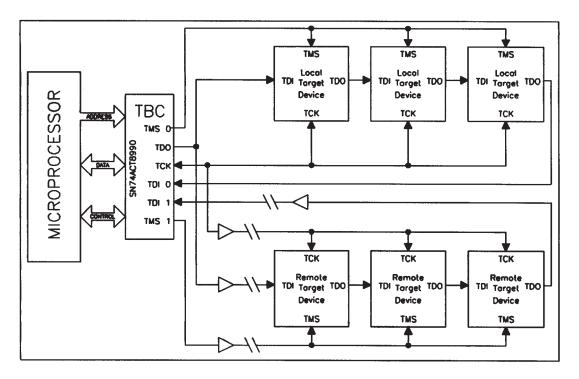

The TDO of several test systems can be connected in parallel and to a TDI input of the TBCs because they are active only during the shift operation (SHIFT-DR, SHIFT-IR) and are otherwise in a high-impedance state. If the test bus signals must be buffered (see Figure 8), the TDO output of the test system can no longer be in the high-impedance state. For this eventuality, two test data inputs (TDI0, TDI1) are available.

Figure 8. Connection of Several IEEE Std 1149.1 Test Buses to the TBC, With Buffering of the Test Bus Signal

### 2.3 Architecture

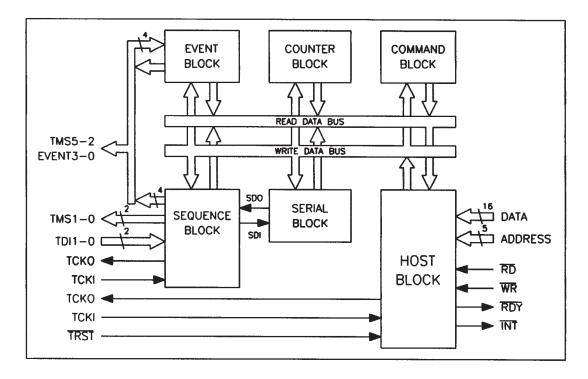

Figure 9 shows the block diagram of the TBC, consisting of six functional blocks:

- Sequence block

- Serial block

- Event block

- Counter block

- Command block

- Host block

Figure 9. Block Diagram of TBC SN74ACT8990

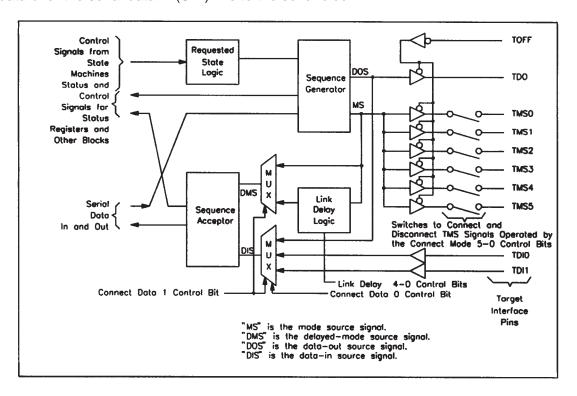

### 2.3.1 Sequence Block

The sequence block (see Figure 10) traces the test system through the status diagram (see Figure 21). During this process, the actual status of the test system is always known. The signals TMS, TDO, and TDI are generated by the sequence block according to IEEE Std 1149.1. During the SHIFT-DR and SHIFT-IR states, it uses the serial data out (SDO) data from the serial block to generate the TDO signal. Additionally, the sequence block transfers the TDI received data over the serial data in (SDI) line to the serial block.

Figure 10. Sequence Block

These programming possibilities are important for the user:

- Choice of the TMS line to be used (TMS0–TMS5)

- Switching of all test bus lines into a high-resistance state

- Choice of the TDI line to be used

- Programmed delay of the test bus signals (link delay)

The link-delay logic allows a simple way to account for flip-flop chains that are switched in the signals TDO, TDI, and TMS between the TBC and the test board (see Figure 11). These flip-flops can be used, for example, to synchronize signals coming from long lines from the TBC SN74ACT8990 to test boards.

Figure 11. Link-Delay Logic

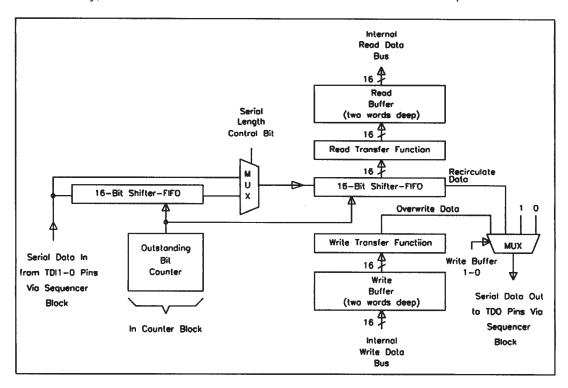

#### 2.3.2 Serial Block

An understanding of the operation of the serial block is an important requirement for the application of the TBC (see Figure 12). The serial block supplies the commands and data that are sent to the IEEE Std 1149.1-compatible test boards in the SHIFT-IR and SHIFT-DR states. In the same way, it collects the bits that are read back from the TDO output of the test board.

Figure 12. Serial Block

The SDO passes through the following sequence block to reach the test board as the TDO signal. The SDO signal can be chosen from the following via the multiplexer MUX2:

- SDO data derives from the WRITE BUFFER.

- Die SDO data derives from the SHIFTER-FIFO.

- SDO data consists only of ones.

- SDO data consists only of zeros.

The microprocessor writes data and commands into the WRITE BUFFER, which are sent to the test board via the SDO output. This WRITE BUFFER consists of two 16-bit registers. If the computer writes a 16-bit word into the first register, this register can be shifted out immediately via SDO. In the meantime, it is possible to write the next 16-bit word into the second register. The functional control of the register – that is, which register is transferring data and which can be addressed by the computer – is automatically performed by the TBC. The user must only request, via a status register, how many registers of the WRITE BUFFER are empty.

The write transfer function allows the user to choose whether the WRITE BUFFER should be shifted to the right, i.e., starting with the least significant bit (LSB), or to the left, i.e., beginning with the most significant bit (MSB).

The TDI receiver data from the test board first pass through the sequence block, and then are shifted over the SDI into the SHIFTER-FIFO. The SHIFTER-FIFO is a shift register, whose length can be programmed to 16 bits or 32 bits with the help of the multiplexer MUX1. After reset, the SHIFTER-FIFO is loaded with 1s. All bits that leave the SHIFTER FIFO during a shift process are stored in the READ BUFFER.

The READ BUFFER, like the WRITE BUFFER, consists of two 16-bit registers. The operation is similar to that of the WRITE BUFFER; the only difference is that the data flow is in the reverse direction, i.e., the processor reads the data. The processor can determine via a register how many registers of the READ BUFFERs contain data. Because, as explained previously, the SHIFTER-FIFO is loaded with 1s on reset, the first bits that the computer reads from the READ BUFFER are 16 or 32 1s, depending on length to which the SHIFTER-FIFOs have been programmed. Only then will the first bits arrive from the TDI input.

The bit-by-bit transfer of data from the SHIFTER-FIFO to the READ BUFFER is performed by the read transfer function. It allows the user the following programs:

- Bits are transferred from the right into the WRITE BUFFER, with the first transmitted bit as LSB in the WRITE BUFFER.

- Bits are transmitted from the right into the WRITE BUFFER, with the last transmitted bit as LSB in the WRITE BUFFER.

#### 2.3.3 Event Block

With the help of the event block, external events can be used to influence the test program, or transferred to the control computer from the event block as an interrupt. The operation of the event block is only of interest to those users who want to control the test program in accordance with events. If no such control is required, the following section can be skipped.

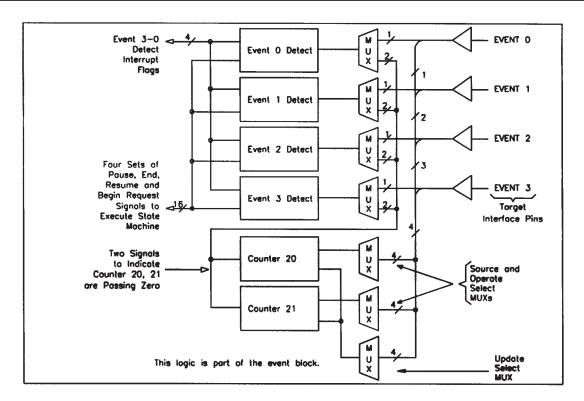

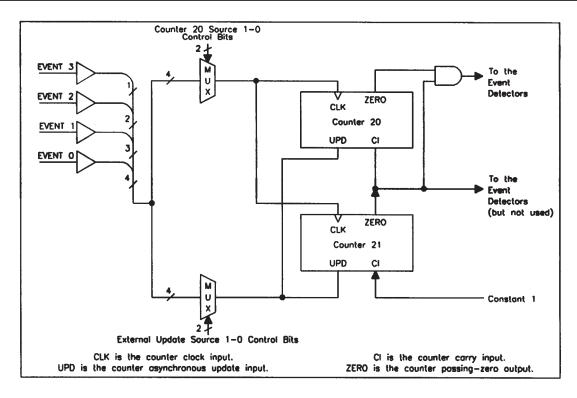

Figure 13 shows the block diagram of the event block inputs. Each input has its own event detector, which reacts on recognizing predetermined events. In addition, the two 16-bit backward counters (COUNTER20 and COUNTER21) are available to count events (see Figure 15). These counters also can be configured as two combined 16-bit counters (see Figure 16) and as a 32-bit counter (see Figure 17). The multiplexers of the event blocks allow the programming of a variety of different functions.

Figure 13. Inputs of the Event Block

For example, the EVENT0 input can be switched directly to the event detector by use of the multiplexer MUX 0. The EVENT DETECTOR 0 is programmed to recognize a particular event, e.g., the arrival of a rising pulse edge. It is, however, also possible to count events that occur at the EVENT0 input only with COUNTER20. After the counter of the COUNTER UPDATE register of the counter blocks (see Figure 18) has been loaded with the required value, on arrival of an event at the EVENT0 input it will be decremented by one. At the zero crossing of COUNTER20, the event detector activates its output.

The control computer has no direct access to COUNTER20 and COUNTER21; however, the COUNTER2 UPDATE register can be written to from the control computer. If COUNTER20 and COUNTER21 are loaded in parallel, this always takes place with the value in the COUNTER2 UPDATE register.

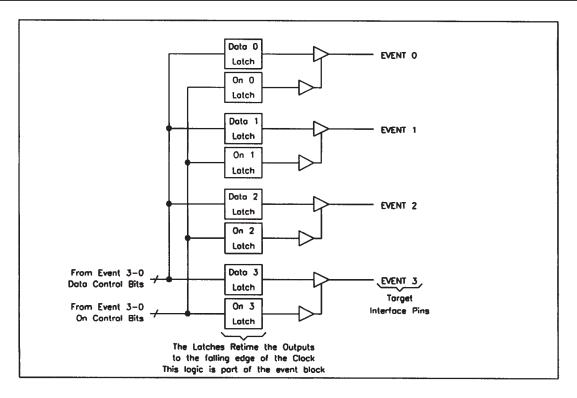

The output circuit of the event block is shown in Figure 14. For each output, two latches are available. One latch stores the required output level, the second latch allows the driver to switch into a high-resistance state and, therefore, to configure the connection as an input.

Figure 14. Outputs of the Event Block

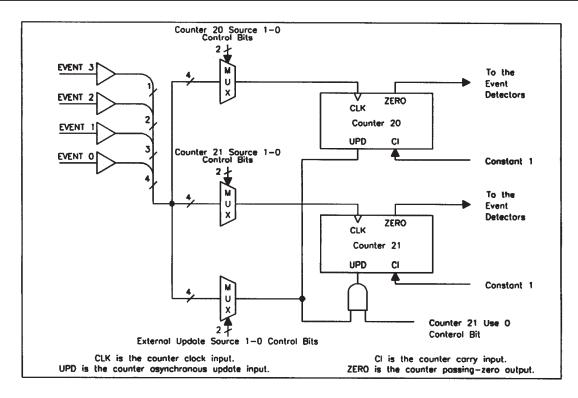

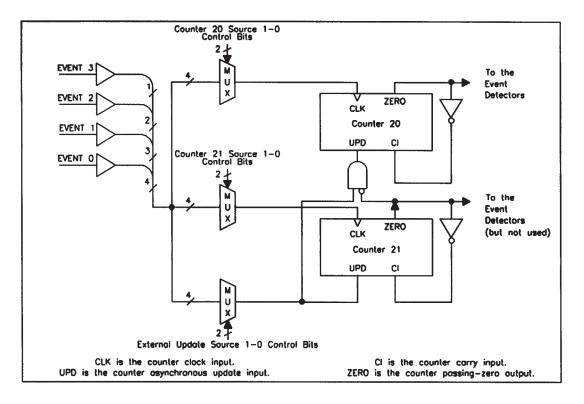

COUNTER20 and COUNTER21 can be configured as follows:

- COUNTER20 and COUNTER21 work as separate 16-bit counters.

- COUNTER20 and COUNTER21 work as combined 16-bit counters. In this case, both

counters are implemented as separate 16-bit counters, but COUNTER20 is loaded from the

COUNTER UPDATE register until COUNTER21 has the first zero crossing. In this case, two

events control the event recognition. For example, it can be programmed so that the first

event must occur 55 times, and then the second event 12,345 times, before the event

detector responds.

- Both counters are connected together to make a 32-bit counter (COUNTER2).

Figure 15. COUNTER20 and COUNTER21 Configured as Separate 16-Bit Counters

Figure 16. COUNTER20 and COUNTER21 Configured as Combined 16-Bit Counters

Figure 17. COUNTER20 and COUNTER21 Configured as One 32-Bit Counter (COUNTER2)

#### 2.3.4 Counter Block

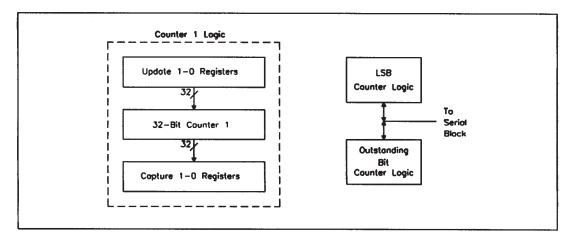

The part of the counter block (see Figure 18) that is relevant for the user consists of:

- COUNTER1 UPDATE register

- 32-bit backwards counter (COUNTER1)

- COUNTER1 CAPTURE register

Figure 18. Counter Block

COUNTER1 is used to count the SHIFT-DR, SHIFT-IR, and RUN-TEST/IDLE states. Also, it is possible to use it to count events. For this purpose, however, COUNTER20 and COUNTER21 are primarily available.

The control computer has no direct access to COUNTER1; it can only write into the COUNTER1 UPDATE register and read the COUNTER1 CAPTURE register. If COUNTER1 is loaded in parallel, this always is done with the value of the COUNTER1 UPDATE register. The actual count state of COUNTER1 can be copied parallel into the COUNTER1 CAPTURE register. From there, the actual count state can pass to the controlling computer.

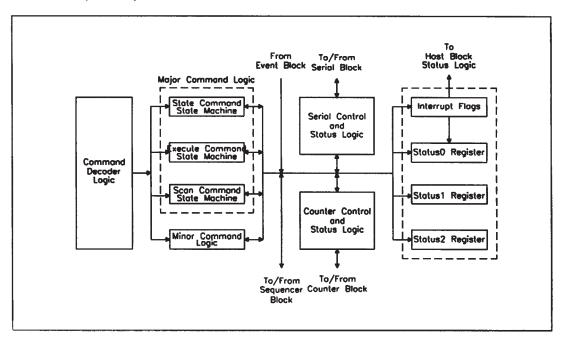

#### 2.3.5 Command Block

The command block contains two command registers (MAJOR COMMAND and MINOR COMMAND) (see Figure 19). In addition, all status registers are part of this block. The command block, with the command decode logic, controls the command process, with no intervention required by the user.

Figure 19. Command Block

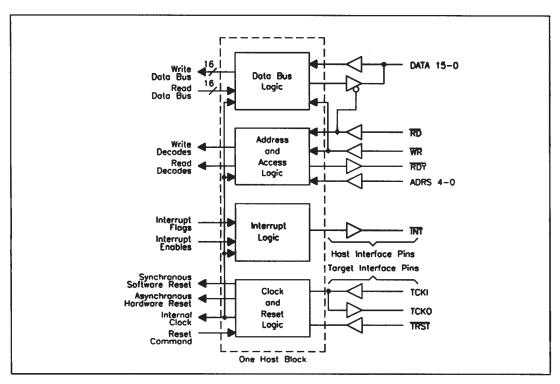

### 2.3.6 Host Block

The tasks of the host block include data-bus signal conditioning, decoding addresses and control lines, and conditioning interrupts for the control computer. In addition, the host block includes the reset logic and the buffering of the test pulse TCK. This block also performs its functions with no intervention required by the user.

Figure 20. Host Block

### 3 Programming

The control computer has access to the functions of the TBC using 24 registers, which are listed in Table 1. The ten control registers configure the TBC. The 32-bit command register is made up of a combination of the MAJOR COMMAND and MINOR COMMAND registers. With the MAJOR COMMAND register, presets of the commands are implemented, while the MINOR COMMAND register controls the execution; the commands are started, interrupted, or terminated. With the four COUNTER UPDATE and two CAPTURE registers, the counters of the event block and the counter block are controlled. The internal state of the TBC can be ascertained over three STATUS registers. The READ BUFFER and WRITE BUFFER are used to exchange data between the test board and the controlling computer.

Table 1. Registers of TBC SN74ACT8990

| ADR | Register Name    | Application                                                                                                     | Access     |

|-----|------------------|-----------------------------------------------------------------------------------------------------------------|------------|

| 00  | CONTROL0         | Interrupt Control Bits                                                                                          | Read/Write |

| 01  | CONTROL1         | Special Function for Production Test                                                                            | Read/Write |

| 02  | CONTROL2         | TMS0 TMS5 Connections                                                                                           | Read/Write |

| 03  | CONTROL3         | TMS/EVENT Function, TDO on/off, TMS/TCK Data Format                                                             | Read/Write |

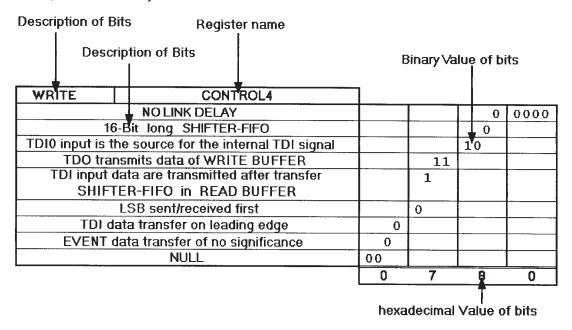

| 04  | CONTROL4         | Delay,<br>Data Format of TDI and TDO pins                                                                       | Read/Write |

| 05  | CONTROL5         | EVENT pins Data Output and Direction                                                                            | Read/Write |

| 06  | CONTROL6         | Event Choice of EVENT0/1 Inputs                                                                                 | Read/Write |

| 07  | CONTROL7         | Event Choice of EVENT2/3 Inputs                                                                                 | Read/Write |

| 08  | CONTROL8         | COUNTER1 Control                                                                                                | Read/Write |

| 09  | CONTROL9         | COUNTER2 Control                                                                                                | Read/Write |

| 0A  | MINOR COMMAND    | Replace Interrupt Flag Bits,<br>Control of Test Run,<br>Read Status, load counters and count,<br>Software RESET | Read/Write |

| 0В  | MAJOR COMMAND    | STATE Command,<br>EXECUTE Command,<br>SCAN Command                                                              | Read/Write |

| 0C  | COUNTER1 UPDATE0 | COUNTER1 Lower Value Word                                                                                       | Read/Write |

| 0D  | COUNTER1 UPDATE1 | COUNTER1 Higher Value Word                                                                                      | Read/Write |

| 0E  | COUNTER2 UPDATE0 | COUNTER2 Lower Value Word<br>or COUNTER20                                                                       | Read/Write |

| 0F  | COUNTER2 UPDATE1 | COUNTER2 Higher Value Words<br>or COUNTER21                                                                     | Read/Write |

| 10  | STATUS0          | Internal States                                                                                                 | Read only  |

| 11  | STATUS1          | External Signals and Requests                                                                                   | Read only  |

| 12  | STATUS2          | State of test board and Buffer                                                                                  | Read only  |

| 13  | STATUS3          | not used                                                                                                        | Read only  |

| 14  | CAPTURE0         | COUNTER1 Lower Value Word                                                                                       | Read only  |

| 15  | CAPTURE1         | COUNTER1 Higher Value Word                                                                                      | Read only  |

| 16  | READ BUFFER      | Input Buffer for TDI                                                                                            | Read only  |

| 17  | WRITE BUFFER     | Output Buffer for TDO                                                                                           | Write only |

### 3.1 Registers

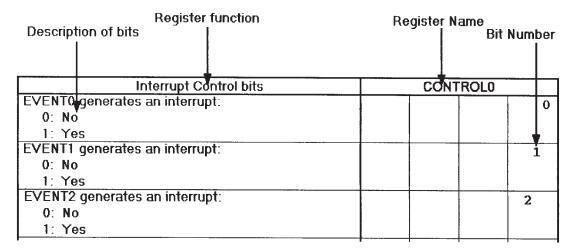

In this section, the individual bits of all registers of the TBC are presented in tables. The table heading includes the register name and a short description of the register function. Within the tables, all bits are described individually. The bit numbers are assembled in groups of four bits each to simplify the presentation in hexadecimal form.

| Interrupt Control bits                            | <u> </u>                                         | CONT | ROL0     |   |

|---------------------------------------------------|--------------------------------------------------|------|----------|---|

| EVENT0 generates an Interrupt:                    |                                                  |      |          | 0 |

| 0: No                                             |                                                  |      |          | Ĭ |

| 1: Yes                                            |                                                  |      |          |   |

| EVENT1 generates an Interrupt:                    |                                                  |      |          | 1 |

| 0: No                                             |                                                  |      |          |   |

| 1: Yes                                            |                                                  |      |          |   |

| EVENT2 generates an Interrupt:                    |                                                  |      |          | 2 |

| 0: No                                             |                                                  |      |          |   |

| 1: Yes                                            |                                                  |      |          |   |

| EVENT3 generates an Interrupt:                    | <del>                                     </del> | ļ    |          | 3 |

| 0: No                                             |                                                  |      |          | ١ |

| 1: Yes                                            |                                                  |      |          |   |

| The COUNTER1 EXECUTE Flag generates an Interrupt: |                                                  |      | 1        |   |

| 0: No                                             |                                                  |      | 4        |   |

| 1: Yes                                            |                                                  |      |          |   |

|                                                   |                                                  |      |          |   |

| The COUNTER1 SCAN Flag generates an Interrupt:    |                                                  |      | 5        |   |

| 0: No                                             |                                                  |      |          |   |

| 1: Yes                                            |                                                  |      |          |   |

| NULL                                              |                                                  |      | 76       |   |

| The SUSPEND Flag generates an Interrupt:          |                                                  | 8    |          |   |

| 0: No                                             |                                                  |      |          |   |

| 1: Yes                                            |                                                  |      |          |   |

| The END Flag generates an Interrupt:              |                                                  | 9    |          |   |

| 0: No                                             |                                                  |      |          |   |

| 1: Yes                                            |                                                  |      |          |   |

| The RESUME Flag generates an Interrupt:           |                                                  | A    |          |   |

| 0: No                                             |                                                  |      |          |   |

| 1: Yes                                            |                                                  |      |          |   |

| The BEGIN SCAN Flag generates an Interrupt:       |                                                  | В    |          |   |

| 0: No                                             |                                                  | ~    |          |   |

| 1: Yes                                            |                                                  |      |          |   |

| The BUFFER ERROR Flag generates an Interrupt:     | С                                                |      |          |   |

| 0: No                                             |                                                  |      |          |   |

| 1: Yes                                            |                                                  |      |          |   |

| The BUFFER READY Flag generates an Interrupt:     | D                                                |      |          |   |

| 0: No                                             |                                                  |      |          |   |

| 1: Yes                                            |                                                  |      |          |   |

| The ABORT Flag generates an Interrupt:            | -                                                |      |          |   |

| No     No                                         | E                                                |      |          |   |

| 1: Yes                                            |                                                  |      |          |   |

|                                                   | <del>  </del>                                    |      | <u> </u> |   |

| The FINISH Flag generates an Interrupt:           | F                                                |      |          |   |

| 0: No                                             |                                                  |      |          |   |

| 1: Yes                                            | L                                                |      |          |   |

| Special Functions for Production Test | CONTROL1 |      |      |      |

|---------------------------------------|----------|------|------|------|

| Each Bit:                             |          |      |      | 3210 |

| 0: Normal operation                   |          |      |      |      |

| Test operation for Production Test    |          |      |      |      |

| Not used                              |          |      | 7554 |      |

| Each Bit:                             | С        | BA98 |      |      |

| 0: Normal operation                   |          |      |      |      |

| Test operation for Production Test    |          |      |      |      |

| Not used                              | FED      |      |      |      |

When using the SN74ACT8990 as controller of a test bus according to IEEE Std 1149.1, all bits of these registers must be set to zero by the user. With the help of these registers, the manufacturer can switch various parts of the component into test operation during production test. This allows a comprehensive, but simple, functional examination of the internal circuitry.

#### CONTROL2

| TMS0 TMS5 Connections                       |      | CONT | ROL2 |   |

|---------------------------------------------|------|------|------|---|

| TMS0 is connected with internal TMS source: |      |      |      | 0 |

| 0: No                                       |      |      |      |   |

| 1: Yes                                      |      |      |      |   |

| TMS1 is connected with internal TMS source: |      |      |      | 1 |

| 0: No                                       |      |      |      |   |

| 1: Yes                                      |      |      |      |   |

| TMS2 is connected with internal TMS source: |      |      |      | 2 |

| 0: No                                       |      |      |      |   |

| 1: Yes                                      |      |      |      |   |

| TMS3 is connected with internal TMS source: |      |      |      | 3 |

| 0: No                                       | 1    |      |      |   |

| 1: Yes                                      |      |      |      |   |

| TMS4 is connected with internal TMS source: |      |      | 4    |   |

| 0: No                                       |      |      |      |   |

| 1: Yes                                      | _    |      |      |   |

| TMS5 is connected with internal TMS source: |      |      | 5    |   |

| 0: No                                       |      |      |      |   |

| 1: Yes                                      |      |      |      |   |

| NULL                                        | FEDC | BA98 | 76   |   |

The component generates a TMS signal internally. This signal can be extracted at the pins TMS0–TMS5. All TMS pins that are not connected to the internal TMS source remain in a static state.

| Function of the TMS/EVENT pins, Data Format of the TMS and TCK pins | CONTROL3 |      |   |   |

|---------------------------------------------------------------------|----------|------|---|---|

| TMS2/EVENTO:                                                        |          |      |   | 0 |

| 0: EVENT Input or Output                                            |          |      |   | 0 |

| 1: TMS2 Output                                                      |          |      |   |   |

| TMS3/EVENT1:                                                        |          |      |   | 1 |

| 0: EVENT Input or Output                                            |          |      |   |   |

| 1: TMS3 Output                                                      | ļ        |      |   |   |

| TMS4/EVENT2:                                                        |          |      |   | 2 |

| 0: EVENT Input or Output                                            |          |      |   | 2 |

| 1: TMS4 Output                                                      |          |      |   |   |

| TMS5/EVENT3:                                                        | 1        |      |   | 3 |

| 0: EVENT Input or Output                                            |          |      |   | _ |

| 1: TMS5 Output                                                      |          |      |   |   |

| TCKO on/off:                                                        |          |      | 4 |   |

| 0: TCKO Output is switched on                                       |          |      |   |   |

| 1: TCKO Output is switched off                                      |          |      |   |   |

| TDO on/off:                                                         |          |      | 5 |   |

| 0: TDO Output is switched on                                        |          |      |   |   |

| 1: TDO Output is switched off                                       | l        |      |   |   |

| TMS on/off:                                                         |          |      | 6 |   |

| 0: all TMS Outputs are switched on                                  |          |      |   |   |

| all TMS Outputs are switched off                                    |          |      |   |   |

| EVENT on/off:                                                       |          |      | 7 |   |

| 0: all EVENT Outputs are switched on                                |          |      |   |   |

| all EVENT Outputs are switched off                                  |          |      |   |   |

| Output Bit Format:                                                  | 1        | BA98 |   |   |

| 0000: for operation to IEEE 1149.1                                  |          |      |   |   |

| else: for operation with special TI components                      |          |      |   |   |

| TCKO Output signal if TCKO Bit D is set to 1:                       | C        |      |   |   |

| 0: static 0-signal                                                  |          |      |   |   |

| 1: static 1-signal                                                  | <u> </u> |      |   |   |

| TCKO Data Format:                                                   | D        |      |   | [ |

| TCKO is connected with internal TCK source                          |          |      |   |   |

| 1: static signal                                                    |          |      |   |   |

| NULL                                                                | FE       |      |   |   |

| Delay, Data Formats of TDI and TDO Pins                  |    | CONT | ROL4 |      |

|----------------------------------------------------------|----|------|------|------|

| Delay:                                                   |    |      | 4    | 3210 |

| 00000 to 11111: with these bits, the LINK DELAY          |    |      |      |      |

| Registers can be set to a delay from                     |    |      |      |      |

| 0 to 31 bits length.                                     |    |      |      |      |

| SHIFTER-FIFO Length:                                     |    |      | 5    |      |

| 0: 16 bits                                               |    |      |      |      |

| 1: 32 bits                                               |    |      |      |      |

| TDI Selection:                                           |    |      | 76   |      |

| 00,                                                      |    |      |      |      |

| 01: The internal TDO signal is the source for the        |    |      |      |      |

| internal signal TDI                                      |    |      |      |      |

| 10: The TDI0 Input is the source for the internal signal |    |      |      |      |

| TDI                                                      |    |      |      |      |

| 11: The TDI1 Input is the source for the internal signal |    |      |      |      |

| TDI                                                      |    |      |      |      |

| TDO Sending Data:                                        |    | 98   |      |      |

| 00: TDO sends 0's                                        |    |      | ĺ    |      |

| 01: TDO sends 1's                                        |    |      |      |      |

| 10: TDO sends data of the SHIFTER-FIFO                   |    |      |      |      |

| 11: TDO sends data of the WRITE BUFFER                   |    |      |      |      |

| READ BUFFER on/off:                                      |    | A    |      |      |

| 0: The received data is ignored after flowing through    |    |      |      |      |

| the SHIFTER-FIFO                                         |    |      |      |      |

| 1: The received data is transferred to the READ          |    |      |      |      |

| BUFFER after flowing through the SHIFTER-FIFO            |    |      |      |      |

| Transfer Format:                                         |    | В    |      |      |

| 0: At data transfer, the LSB is always sent/received     |    |      |      |      |

| first                                                    |    |      |      |      |

| 1: At data transfer, the MSB is always sent/received     |    |      |      |      |

| first                                                    |    |      |      |      |

| TDI Data Transfer:                                       | С  |      |      |      |

| 0: TDI Data Transfer on leading edge                     |    |      |      |      |

| 1: TDI Data Transfer on trailing edge                    |    |      |      |      |

| EVENT Data Transfer:                                     | D  |      |      |      |

| 0: EVENT Data Transfer on leading edge                   |    | -    |      |      |

| EVENT Data Transfer on trailing edge                     |    |      |      |      |

| NULL                                                     | FE |      |      |      |

| EVENT Pins Output Data and Direction of Flow | CONTROL5 |   |      |   |

|----------------------------------------------|----------|---|------|---|

| EVENT0 Output Data:                          |          |   |      | 0 |

| 0: 0-Level                                   |          |   |      |   |

| 1: 1-Level                                   |          |   |      |   |

| EVENT1 Output Data:                          |          |   |      | 1 |

| 0: 0-Level                                   |          |   |      |   |

| 1: 1-Level                                   |          |   |      |   |

| EVENT2 Output Data:                          |          |   |      | 2 |

| 0: 0-Level                                   |          |   |      |   |

| 1: 1-Level                                   |          |   |      |   |

| EVENT3 Output Data:                          |          |   |      | 3 |

| 0: 0-Level                                   |          |   |      |   |

| 1: 1-Level                                   |          |   |      |   |

| NULL                                         |          |   | 7654 |   |

| EVENT0 Data Flow Direction:                  |          | 8 |      |   |

| 0: EVENT0 is an input                        |          |   |      |   |

| 1: EVENT0 is an output                       |          |   |      |   |

| EVENT1 Data Flow Direction:                  |          | 9 |      |   |

| 0: EVENT1 is an input                        |          |   |      |   |

| 1: EVENT1 is an output                       |          |   |      |   |

| EVENT2 Data Flow Direction:                  |          | A |      |   |

| 0: EVENT2 is an input                        |          |   |      |   |

| 1: EVENT2 is an output                       |          |   |      |   |

| EVENT3 Data Flow Direction:                  |          | В |      |   |

| 0: EVENT3 is an input                        |          |   |      |   |

| 1: EVENT3 is an output                       |          |   |      |   |

| NULL                                         | FEDC     |   |      |   |

| Event Choice at the EVENT0/1 Inputs                            |   | CONT | ROL6 |   |

|----------------------------------------------------------------|---|------|------|---|

| EVENT0 sets the SUSPEND REQUEST Flag:                          |   |      |      | 0 |

| 0: No                                                          |   |      |      |   |

| 1: Yes                                                         |   |      |      |   |

| EVENT0 sets the END REQUEST Flag:                              |   |      |      | 1 |

| 0: No                                                          |   |      |      |   |

| 1: Yes                                                         |   |      |      |   |

| EVENT0 sets the RESUME REQUEST Flag:                           |   |      |      | 2 |

| 0: No<br>1: Yes                                                |   |      |      |   |

| EVENT0 sets the BEGIN REQUEST Flag:                            |   |      |      | 3 |

| 0: No                                                          |   |      |      | 3 |

| 1: Yes                                                         |   |      |      |   |

| EVENT0 is synchronous or asynchronous:                         |   |      | 4    |   |

| 0: The recognition of the EVENT0 is asynchronous               |   |      | -    |   |

| The recognition of the EVENT0 is synchronous                   |   |      |      |   |

| EVENT0 Masking:                                                |   |      | 5    |   |

| 0: The recognition of the EVENT0 always occurs                 |   |      |      |   |

| 1: No EVENTO recognition during CAPTURE-DR,                    |   |      |      |   |

| SHIFT-DR, EXIT1-DR, PAUSE-DR, EXIT2-DR,                        |   |      |      |   |

| CAPTURE-IR, SHIFT-IR, EXIT1-IR, PAUSE-IR,                      |   |      |      |   |

| EXIT2-IR                                                       |   |      |      |   |

| Asynchronous EVENT0 recognition:                               |   |      | 76   |   |

| 00: Trailing Edge at Input EVENT0                              |   |      |      |   |

| 01: Leading Edge at Input EVENT0                               |   |      |      |   |

| 10: Zero passing of COUNTER20                                  |   |      |      |   |

| 11: Zero passing of COUNTER21                                  |   |      |      |   |

| Synchronous EVENT0 recognition of 2 successive TCK edges:      |   |      |      |   |

| 00: 1-Level> 0-Level                                           |   |      |      |   |

| 01: 0-Level> 1-Level                                           |   |      |      |   |

| 10: 0-Level> 0-Level                                           |   |      |      |   |

| 11: 1-Level> 1-Level                                           |   |      |      |   |

| EVENT1 sets the SUSPEND REQUEST Flag:                          |   | 8    |      |   |

| 0: No                                                          |   |      |      |   |

| 1: Yes                                                         |   |      |      |   |

| EVENT1 sets the END REQUEST Flag:                              |   | 9    |      |   |

| 0: No                                                          |   | -    |      |   |

| 1: Yes                                                         |   |      |      |   |

| EVENT1 sets the RESUME REQUEST Flag:                           |   | А    |      |   |

| 0: No                                                          |   |      |      |   |

| 1: Yes                                                         |   |      |      |   |

| EVENT1 sets the BEGIN REQUEST Flag:                            |   | В    |      |   |

| 0: No                                                          |   |      |      |   |

| 1: Yes                                                         |   |      |      |   |

| EVENT1 is synchronous or asynchronous:                         | С |      |      |   |

| 0: The recognition of the EVENT1 is asynchronous               |   |      |      |   |

| 1: The recognition of the EVENT1 is synchronous                |   |      |      |   |

| EVENT1 Masking: 0: The recognition of the EVENT1 always occurs | D | [    |      |   |

| 1: No EVENT1 recognition during CAPTURE-DR,                    |   |      |      |   |

| SHIFT-DR, EXIT1-DR, PAUSE-DR, EXIT2-DR,                        |   |      |      |   |

| CAPTURE-IR, SHIFT-IR, EXIT1-IR, PAUSE-IR,                      |   |      |      |   |

| EXIT2-IR                                                       | 1 |      |      |   |

| E/(112 11)                                                     | L | L    | 1    | L |

# CONTROL6 (Continued)

| Asynchronous EVENT1 recognition:                   | FE |  |  |

|----------------------------------------------------|----|--|--|

| 00: Trailing Edge at input EVENT1                  |    |  |  |

| 01: Leading Edge at input EVENT1                   |    |  |  |

| 10: Zero passing of COUNTER20                      |    |  |  |

| 11: Zero passing of COUNTER21                      |    |  |  |

| Synchronous EVENT1 recognition of 2 successive TCK |    |  |  |

| edges:                                             |    |  |  |

| 00: 1-Level> 0-Level                               |    |  |  |

| 01: 0-Level> 1-Level                               |    |  |  |

| 10: 0-Level> 0-Level                               |    |  |  |

| 11: 1-Level> 1-Level                               |    |  |  |

| Event Choice of the EVENT2/3 Inputs                                                            |     | CONT | ROL7     |   |

|------------------------------------------------------------------------------------------------|-----|------|----------|---|

| EVENT2 sets the SUSPEND REQUEST Flag:                                                          |     |      |          | 0 |

| 0: No                                                                                          |     |      |          |   |

| 1: Yes                                                                                         |     |      |          |   |

| EVENT2 sets the END REQUEST Flag:                                                              |     |      |          | 1 |

| 0: No                                                                                          |     |      |          |   |

| 1: Yes                                                                                         |     |      |          |   |

| EVENT2 sets the RESUME REQUEST Flag:                                                           |     |      |          | 2 |

| 0: No<br>1: Yes                                                                                |     |      |          | 1 |

|                                                                                                |     |      |          | _ |

| EVENT2 sets the BEGIN REQUEST Flag: 0: No                                                      |     |      |          | 3 |

| 1: Yes                                                                                         |     |      |          |   |

| EVENT2 is synchronous or asynchronous:                                                         |     |      | 4        |   |

| 0: The recognition of the EVENT2 is asynchronous                                               |     |      | 4        |   |

| The recognition of the EVENT2 is asynchronous     The recognition of the EVENT2 is synchronous |     |      |          |   |

| EVENT2 Masking:                                                                                |     |      | 5        |   |

| 0: The recognition of the EVENT2 always occurs                                                 |     |      |          |   |

| 1: No EVENT2 recognition during CAPTURE-DR,                                                    |     |      | -        |   |

| SHIFT-DR, EXIT1-DR, PAUSE-DR, EXIT2-DR,                                                        |     |      |          |   |

| CAPTURE-IR, SHIFT-IR, EXIT1-IR, PAUSE-IR,                                                      |     |      |          |   |

| EXIT2-IR                                                                                       |     |      |          |   |

| Asynchronous EVENT2 recognition:                                                               |     |      | 76       |   |

| 00: Trailing Edge at input EVENT2                                                              |     |      | ' '      |   |

| 01: Leading Edge at input EVENT2                                                               |     | }    |          |   |

| 10: Zero passing of COUNTER20                                                                  |     |      |          |   |

| 11: Zero passing of COUNTER21                                                                  |     |      |          |   |

| Synchronous EVENT2 recognition of 2 successive TCK                                             |     |      |          |   |

| edges:                                                                                         |     |      |          |   |

| 00: 1-Level> 0-Level                                                                           |     |      |          |   |

| 01: 0-Level> 1-Level                                                                           |     |      |          |   |

| 10: 0-Level> 0-Level                                                                           |     |      |          |   |

| 11: 1-Level> 1-Level                                                                           |     |      |          |   |

| EVENT3 sets the SUSPEND REQUEST Flag:                                                          |     | 8    |          |   |

| 0: No                                                                                          |     |      |          |   |

| 1: Yes                                                                                         |     |      |          |   |

| EVENT3 sets the END REQUEST Flag:                                                              |     | 9    |          |   |

| 0: No                                                                                          |     |      |          |   |

| 1: Yes                                                                                         |     |      |          |   |

| EVENT3 sets the RESUME REQUEST Flag:                                                           |     | A    |          |   |

| 0: No                                                                                          |     | ļ    |          |   |

| 1: Yes                                                                                         |     | B    |          |   |

| EVENT3 sets the BEGIN REQUEST Flag: 0: No                                                      |     | В    |          |   |

| 1: Yes                                                                                         |     |      |          |   |

| EVENT3 is synchronous or asynchronous:                                                         | C   |      | <u> </u> | - |

| 0: The recognition of the EVENT3 is asynchronous                                               |     |      |          |   |

| The recognition of the EVENT3 is asynchronous     The recognition of the EVENT3 is synchronous |     |      |          |   |

| EVENT3 Masking:                                                                                | D   |      |          |   |

| 0: The recognition of the EVENT3 always occurs                                                 | ا ا |      |          |   |

| 1: No EVENT3 recognition during CAPTURE-DR,                                                    |     |      |          |   |

| SHIFT-DR, EXIT1-DR, PAUSE-DR, EXIT2-DR,                                                        |     |      | ]        |   |

| CAPTURE-IR, SHIFT-IR, EXIT1-IR, PAUSE-IR,                                                      |     |      | [        |   |

| EXIT2-IR                                                                                       |     |      |          |   |

|                                                                                                |     |      |          |   |

# CONTROL7 (Continued)

| asynchronous EVENT3 recognition:                   | FE |   |  |

|----------------------------------------------------|----|---|--|

| 00: Trailing Edge at input EVENT3                  |    |   |  |

| 01: Leading Edge at input EVENT3                   |    |   |  |

| 10: Zero passing of COUNTER20                      |    |   |  |

| 11: Zero passing of COUNTER21                      |    |   |  |

| synchronous EVENT3 recognition of 2 successive TCK |    |   |  |

| edges:                                             |    | ļ |  |

| 00: 1-Level> 0-Level                               |    |   |  |

| 01: 0-Level> 1-Level                               |    |   |  |

| 10: 0-Level> 0-Level                               |    |   |  |

| 11: 1-Level> 1-Level                               |    |   |  |

| COUNTER1 Control                                          |      | CONT    | ROL8 |   |

|-----------------------------------------------------------|------|---------|------|---|

| COUNTER1 sets the SUSPEND REQUEST Flag during             |      |         |      | 0 |

| zero passing:                                             |      |         |      |   |

| 0: No                                                     |      |         |      |   |

| 1: Yes                                                    |      |         |      |   |

| COUNTER1 sets the END REQUEST Flag during zero            |      |         |      | 1 |

| passing:                                                  |      |         |      |   |

| 0: No                                                     |      |         |      |   |

| 1: Yes                                                    |      |         |      |   |

| COUNTER1 is loaded by the COUNTER1 UPDATE                 |      |         |      | 2 |

| Register during zero passing:                             |      |         |      |   |

| 0: No                                                     |      |         |      |   |

| 1: Yes                                                    |      |         |      |   |

| COUNTER 1 counts                                          |      |         | 54   | 3 |

| 000,                                                      |      |         |      |   |

| 001: never.                                               |      |         |      |   |

| 010: the clock edge of TCK in RUN-TEST/IDLE state         |      |         |      |   |

| during an EXECUTE command.                                |      |         |      |   |

| 011: always when an EXECUTE command is executed.          |      |         | !    |   |

| 100,                                                      |      |         |      |   |

| 101: with the EVENT DETECTOR, which is selected with      |      |         |      |   |

| Bits 7 and 6.                                             |      |         |      |   |

| 110: if an 0-Level exists at the EVENT PIN selected by    |      |         |      |   |

| Bits 7 and 6.                                             |      |         |      |   |

| 111: if an 1-Level exits at the EVENT PIN selected by     |      |         |      |   |

| Bits 7 and 6.                                             |      |         |      |   |

| COUNTER1 reacts on                                        |      |         | 76   |   |

| 00: EVENT DETECTOR0 or the input EVENT0                   |      |         |      |   |

| 01: EVENT DETECTOR1 or the input EVENT1                   |      |         |      |   |

| 10: EVENT DETECTOR2 or the input EVENT2                   |      |         |      |   |

| 11: EVENT DETECTOR3 or the input EVENT3                   |      |         |      |   |

| if the Bits 5 and 4 have the value 100,101,110 or 111. In |      |         |      |   |

| all other cases the value of these bits is without        |      |         |      |   |

| significance.                                             | FFFC | D 7 0 0 |      |   |

| not used                                                  | FEDC | BA98    |      |   |

| COUNTER2 Control                                                    |         | CONT  | ROL9     |     |

|---------------------------------------------------------------------|---------|-------|----------|-----|

| COUNTER2 is loaded with an                                          |         | 20141 | IVOLD    | 210 |

| 000: 0-Level at the EVENT0 Input.                                   |         |       |          | 710 |

| 001: 1-Level at the EVENTO Input.                                   |         |       |          |     |

| 010: 0-Level at the EVENT1 Input.                                   |         |       |          |     |

| 011: 1-Level at the EVENT1 Input.                                   |         |       |          |     |

| 100: 0-Level at the EVENT2 Input.                                   |         |       |          |     |

|                                                                     |         |       |          |     |

| 101: 1-Level at the EVENT2 Input.                                   |         |       |          |     |

| 110: 0-Level at the EVENT3 Input. 111: 1-Level at the EVENT3 Input. |         |       |          |     |

|                                                                     |         |       |          | _   |

| COUNTER20 is loaded by the COUNTER2 UPDATE0                         |         |       |          | 3   |

| Register: 0: Yes                                                    |         |       |          |     |

|                                                                     |         |       |          |     |

| 1: No                                                               |         |       |          |     |

| COUNTER20 is loaded during zero passing:                            |         |       | 4        |     |

| 0: No                                                               |         |       |          |     |

| 1: Yes                                                              |         |       |          |     |

| COUNTER20 counts                                                    |         |       | 765      |     |

| 000: if there is a trailing edge at the input EVENT0.               |         |       |          |     |

| 001: if there is a leading edge at the input EVENT0.                |         |       |          |     |

| 010: if there is a trailing edge at the input EVENT1.               |         |       |          |     |

| 011: if there is a leading edge at the input EVENT1.                |         |       |          |     |

| 100: if there is a trailing edge at the input EVENT2.               |         |       |          |     |

| 101: if there is a leading edge at the input EVENT2.                |         |       |          |     |

| 110: if there is a trailing edge at the input EVENT3.               |         |       |          |     |

| 111: if there is a leading edge at the input EVENT3.                |         |       |          |     |

| COUNTER2 can be loaded by an                                        |         | 8     |          |     |

| 0: asynchronous signal at the EVENT input.                          | 1       |       |          |     |

| synchronous signal at the EVENT input.                              | l       |       |          |     |

| COUNTER20 and COUNTER21 work as                                     |         | A9    |          |     |

| 00: separate 16-Bit counters; only COUNTER20 can be                 |         |       |          |     |

| loaded by an asynchronous input signal.                             | 1       |       |          |     |

| 01: separate 16-Bit counters; both counters can be                  |         |       |          |     |

| loaded by an asynchronous input signal.                             |         |       |          |     |

| 10: two tied 16-Bit counter                                         |         |       |          |     |

| 11: one 32-Bit counter. This counter can be loaded by               | İ       |       |          |     |

| an asynchronous input signal.                                       |         |       |          |     |

| COUNTER21 is loaded by the COUNTER2 UPDATE1                         |         | В     | <u> </u> |     |

| Register:                                                           |         | 1     |          |     |

| 0: Yes                                                              |         |       |          |     |

| 1: No                                                               |         |       |          |     |

| COUNTER21 is loaded at zero passing:                                | C       |       |          |     |

| 0: No                                                               |         |       |          |     |

| 1: Yes                                                              |         |       |          |     |

| COUNTER21 counts                                                    | FED     |       |          |     |

|                                                                     | LED     |       |          |     |

| 000: if there is a trailing edge at the input EVENTO.               |         |       |          |     |

| 001: if there is a leading edge at the input EVENTO.                |         |       |          |     |

| 010: if there is a trailing edge at the input EVENT1.               | 1       |       |          |     |

| 011: if there is a leading edge at the input EVENT1.                |         |       |          |     |

| 100: if there is a trailing edge at the input EVENT2.               |         |       |          |     |

| 101: if there is a leading edge at the input EVENT2.                |         |       |          | }   |

| 110: if there is a trailing edge at the input EVENT3.               |         |       |          |     |

| 111: if there is a leading edge at the input EVENT3.                | <u></u> |       |          |     |

# **MINOR COMMAND**

| Replace Interrupt Flag Bit 8 to 15          | IV   | MINOR COMMAND |   |   |

|---------------------------------------------|------|---------------|---|---|

| Set/Reset the Interrupt Flag Bit 8:         |      |               |   | 0 |

| 0: No                                       | l l  |               |   |   |

| 1: Yes                                      |      |               |   |   |

| Set/Reset the Interrupt Flag Bit 9:         |      |               |   | 1 |

| 0: No                                       | :    |               |   |   |

| 1: Yes                                      | 1    |               |   |   |

| Set/Reset the Interrupt Flag Bit 10:        |      |               |   | 2 |

| 0: No                                       |      |               |   |   |

| 1: Yes                                      |      |               |   |   |

| Set/Reset the Interrupt Flag Bit 11:        |      |               |   | 3 |

| 0: No                                       |      |               |   |   |

| 1: Yes                                      |      |               |   |   |

| Set/Reset the Interrupt Flag Bit 12:        |      |               | 4 |   |

| 0: No                                       |      |               |   |   |

| 1: Yes                                      |      |               |   |   |

| Set/Reset the Interrupt Flag Bit 13:        |      |               | 5 |   |

| 0: No                                       |      |               |   |   |

| 1: Yes                                      |      |               |   |   |

| Set/Reset the Interrupt Flag Bit 14:        |      |               | 6 |   |

| 0: No                                       |      |               |   |   |

| 1: Yes                                      |      |               |   |   |

| Set/Reset the Interrupt Flag Bit 15:        |      |               | 7 |   |

| 0: No                                       |      | ļ             |   |   |

| 1: Yes                                      |      |               |   |   |

| NULL                                        |      | BA98          |   |   |

| 0001: Reset the Interrupt Flag Bits 8 to 15 | FEDC |               |   |   |

| 0011: Set the Interrupt Flag Bits 8 to 15   |      |               |   |   |

| Replace Interrupt Flag Bits 0 to 5         | N    | MINOR COMMAND |    |   |

|--------------------------------------------|------|---------------|----|---|

| Set/Reset the Interrupt Flag Bit 0:        |      |               |    | 0 |

| 0: No                                      |      |               |    |   |

| 1: Yes                                     |      |               |    |   |

| Set/Reset the Interrupt Flag Bit 1:        |      |               |    | 1 |

| 0: No                                      |      |               |    |   |

| 1: Yes                                     |      |               |    |   |

| Set/Reset the Interrupt Flag Bit 2:        |      |               |    | 2 |

| 0: No                                      |      |               |    |   |

| 1: Yes                                     |      |               |    |   |

| Set/Reset the Interrupt Flag Bit 3:        |      |               |    | 3 |

| 0: No                                      |      |               |    |   |

| 1: Yes                                     |      |               |    |   |

| Set/Reset the Interrupt Flag Bit 4:        |      |               | 4  |   |

| 0: No                                      |      |               |    |   |

| 1: Yes                                     |      |               |    |   |

| Set/Reset the Interrupt Flag Bit 5:        |      |               | 5  |   |

| 0: No                                      |      |               |    |   |

| 1: Yes                                     | 1    |               |    |   |

| NULL                                       |      | BA98          | 76 |   |

| 0000: Reset the Interrupt Flag Bits 0 to 5 | FEDC |               |    |   |

| 0010: Set the Interrupt Flag Bits 0 to 5   |      |               |    |   |

| Controlling the Test Operation                    | MINOR COMMAND |      |   |   |

|---------------------------------------------------|---------------|------|---|---|

| Set/Reset the SUSPEND REQUEST Flag:               |               |      |   | 0 |

| 0: No                                             | l             |      |   |   |

| 1: Yes                                            | l             |      |   |   |

| Set/Reset the END REQUEST Flag:                   |               |      |   | 1 |

| 0: No                                             | l             |      |   |   |

| 1: Yes                                            |               |      |   |   |

| Set/Reset the RESUME REQUEST Flag:                |               |      |   | 2 |

| 0: No                                             |               |      |   |   |

| 1: Yes                                            |               |      |   |   |

| Set/Reset the BEGIN REQUEST Flag:                 |               |      |   | 3 |

| 0: No                                             |               |      |   |   |

| 1: Yes                                            |               |      |   |   |

| NULL                                              |               |      | 4 |   |

| Enable start of an EXECUTE Command:               |               |      | 5 |   |

| 0: No                                             |               |      |   |   |

| 1: Yes                                            |               |      |   |   |

| Canceling a SCAN or EXECUTE Command:              |               |      | 6 |   |

| 0: No                                             | Í             |      |   |   |

| 1: Yes                                            |               |      |   |   |

| Enable start of a STATE, SCAN or EXECUTE Command: | l             |      | 7 |   |

| 0: No                                             | ļ             |      |   |   |

| 1: Yes                                            |               |      |   |   |

| NULL                                              |               | BA98 |   |   |

| 0100: Bits 0 to 3 reset the Flags                 | FEDC          |      |   |   |

| 0101: Bits 0 to 3 set the Flags                   |               |      |   |   |

| Read status, load counter, and count            | MINOR COMMAND |      |   | D |

|-------------------------------------------------|---------------|------|---|---|

| Load COUNTER1 UPDATE into COUNTER1:             |               |      |   | 0 |

| 0: No                                           |               |      |   |   |

| 1: Yes                                          |               |      |   |   |

| Count COUNTER1:                                 |               |      |   | 1 |

| 0: No                                           |               |      |   |   |

| 1: Yes                                          |               |      |   |   |

| Load COUNTER1 into the CAPTURE status register: |               |      |   | 2 |

| 0: No                                           |               |      |   |   |

| 1: Yes                                          |               |      |   |   |

| NULL                                            |               |      |   | 3 |

| Load COUNTER2 UPDATE0 into COUNTER20:           |               |      | 4 |   |

| 0: No                                           |               |      |   |   |

| 1: Yes                                          |               |      |   |   |

| Load COUNTER2 UPDATE1 into COUNTER21:           |               |      | 5 |   |

| 0: No                                           |               |      |   |   |

| 1: Yes                                          |               |      |   |   |

| Refresh STATUS0, STATUS1 and STATUS2 registers: |               |      | 6 |   |

| 0: No                                           |               |      |   |   |

| 1: Yes                                          |               |      |   |   |

| NULL                                            |               | BA98 | 7 |   |

| 0110: Read status, load counter, and count      | FEDC          |      |   |   |

| Software RESET                      | N    | MINOR COMMAND |      |   |

|-------------------------------------|------|---------------|------|---|

| Reset complete 'ACT8990:            |      |               |      | 0 |

| 0: No                               |      |               |      |   |

| 1: Yes                              | ]    |               |      |   |

| Reset interrupt flags:              |      |               |      | 1 |

| 0: No                               |      |               |      |   |

| 1: Yes                              |      |               |      |   |

| Reset READ BUFFER and WRITE BUFFER: |      |               |      | 2 |

| 0: No                               |      |               |      |   |

| 1: Yes                              |      |               |      |   |

| Reset REQUEST flags:                |      |               |      | 3 |

| 0: No                               |      |               |      |   |