# **Calorimeter Trigger**

# **Calorimeter Trigger Overview**

CMS

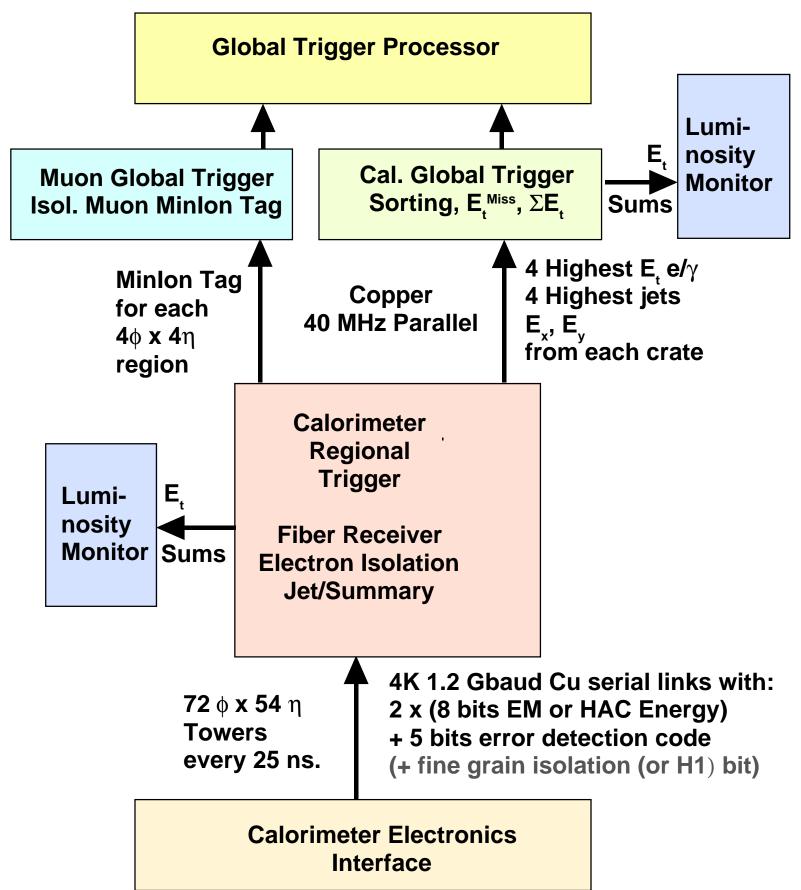

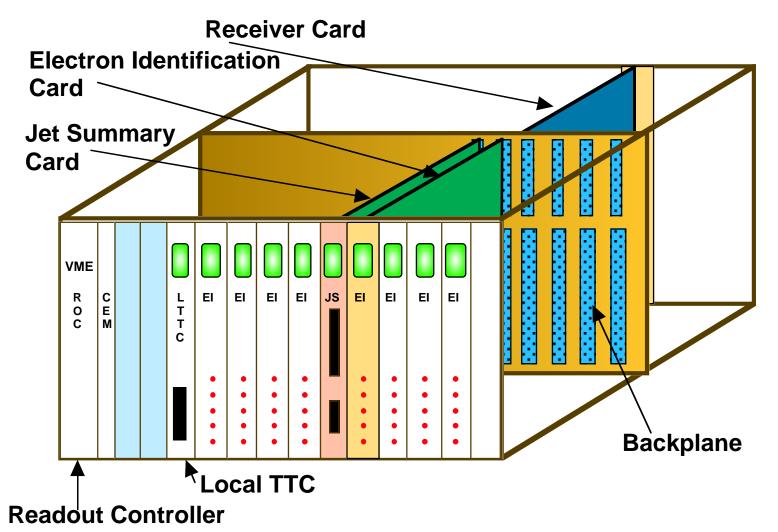

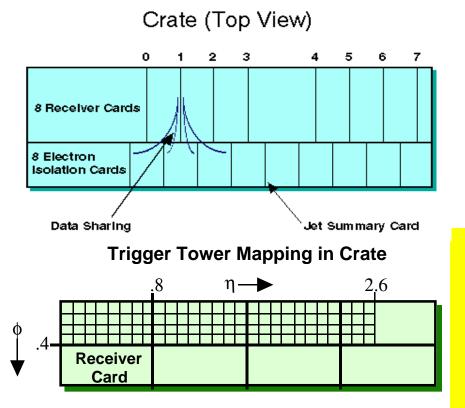

# **Regional Calorimeter Crate**

#### Data from calorimeter FE on Cu links @ 1.2 Gbaud

Into rear-mounted Receiver Cards

#### **160 MHz point to point backplane**

Receiver, Electron Identification, Jet Summary Cards Operate @ 160 MHz

#### **Output to calorimeter global trigger**

### From Jet Summary Card

#### Min Ion and Quiet bits to muon trigger

CMS

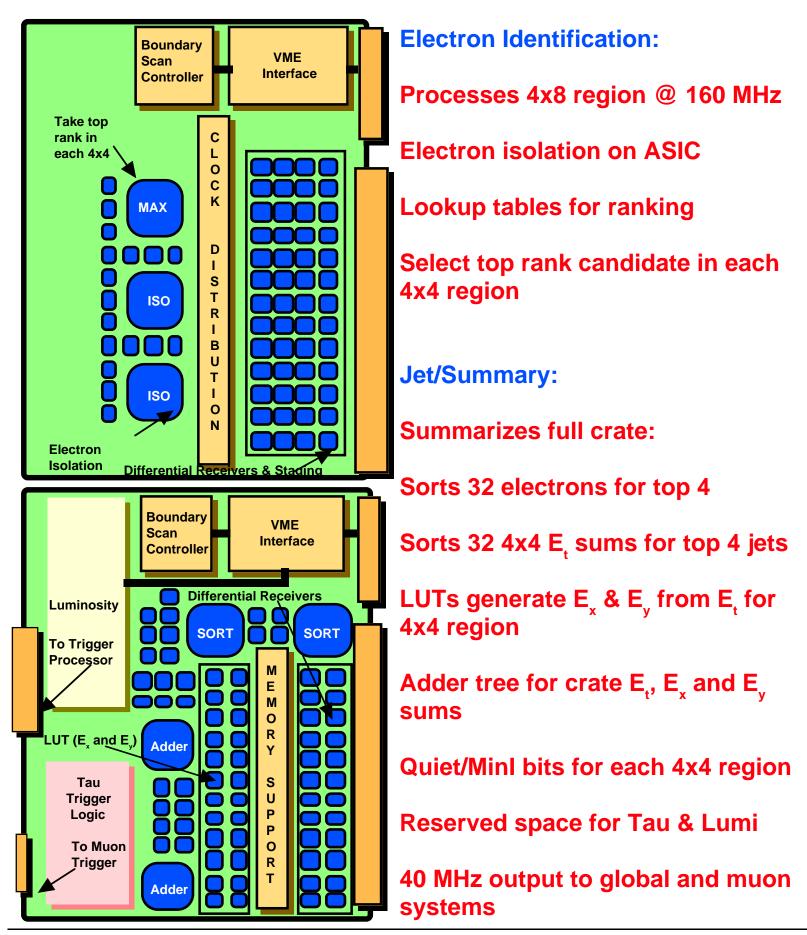

# **Receiver Card Function**

Design optimized to forward data for further processing only at appropriate resolution and only on need-to-know basis.

#### **Receiver card**

- Receives 8-bit non-linear E<sub>t</sub> + 1-bit ID data from 32 ECAL & corresponding HCAL trigger towers.

- Linearizes ECAL & HCAL E<sub>t</sub> & prepares data for subsequent processing by Electron ID Card.

- Stages this & neighbor tower data to Elec. ID card.

- Linearizes ECAL and HCAL E<sub>t</sub> on 8-bit scale and uses Adder ASIC to make 4x4 sums for jet and missing E<sub>t</sub> triggers.

- ORs ECAL fine-grain EM ID and HCAL Muon ID bits separately for each 4x4 region.

- Stages 4x4 region data to Jet/Summary cards.

### **Receiver Card**

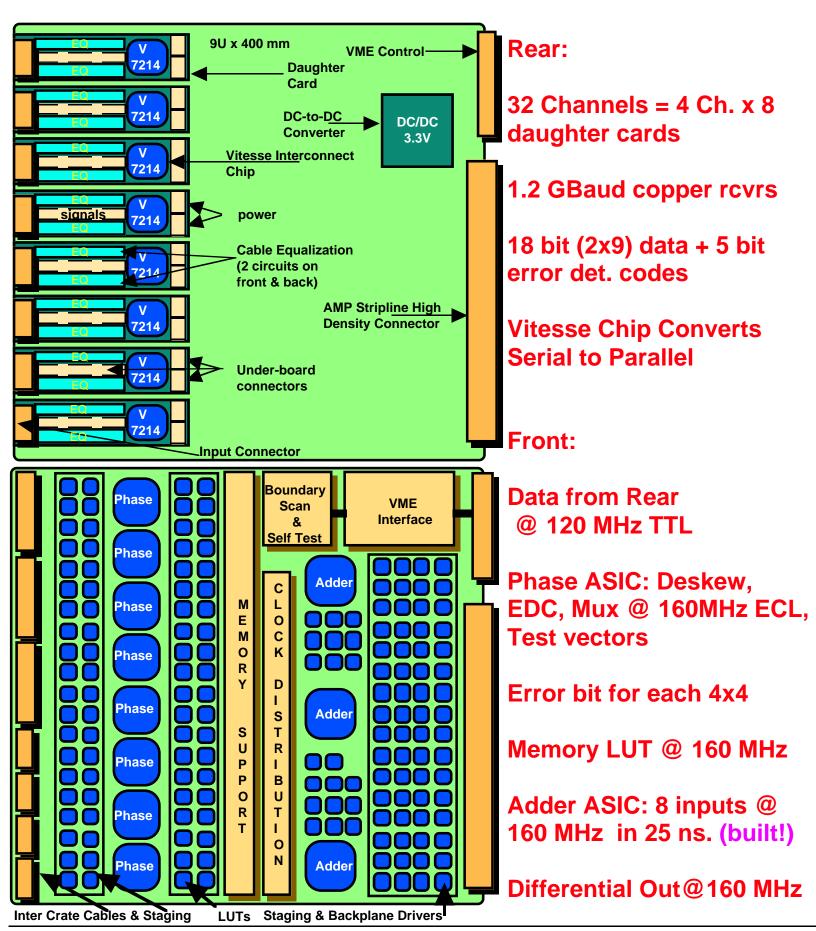

# **Cu Data Link Specification**

Support for 64 E/HCAL ch. per Receiver card. Same technology for both E/HCAL (32 ch. each) 2 channels per copper link:

- Use 24-bit frame to get better trigger energy resolution than 21-bit G-Link frame

- 18-bit data + 5-bit error detection code

- 8-bit energy + 1-bit fine-grain ID per channel

- Error detection bits are necessary for error logging and to zero problem channels that can cause high spurious trigger rate.

- 24-bit word with 8/10-bit encoding implies 1.2 GHz serial link.

- Non-halogenated candidate cables are available. (Cable development being pushed by 1000BaseT ethernet).

Agreement w/HCAL to limit link length at 20m.

4 links per connector: one per daughter card

4 links per Vitesse VSC7214 per daughter card

Channel grouping must match between E/HCAL.

Data across all channels (ECAL & HCAL) should be synchronized for both trigger primitive extraction and DAQ readout.

Data transmitted on equal length cables. Limited phase adjust allowed on Receiver card.

### **Electron ID & Jet/Summary Cards**

Wesley Smith, U. Wisconsin

# **Calorimeter Trigger Status**

### 13 x 8 bit Adder ASIC tested > 160 MHz

### **Receiver Card**

• Designed for 160 MHz

Being built

# Backplane for VME & trigger data

- Prototype constructed

- Prototype Clock & Control Card built

- Signal performance excellent @ 160 MHz

- Confirmation of design feasibility

# **Receiver Card Prototype**

# Front side: Includes almost all features listed in the conceptual design.

### **Rear side: Serial input handling**

- Change in calorimeter electronics location enabled consideration of copper links for transmission btw. calorimeter electronics & level-1 trigger crates in control room.

- Change in receiver card prototype to include feasibility study of Vitesse 7214 communication chips & associated copper cable plant.

- To retain flexibility with testing and to separate data link revisions from the rest of the receiver card, the data link circuitry placed on daughter cards.

- Since special test circuitry has been removed from the final Receiver Card, it is placed on a separate Test Card which the daughter cards also plug into.

### Front (Bkpl. I/O & Adder ASIC tests)

• Submitted for Manufacture

### Rear (Serial copper connection test)

- Equalization network designed & simulated for 20m cable

- Circuit is placed on a daughter card

- Evaluation circuit for the Vitesse 7214 chip is designed and laid out

- Testing circuit is moved to a "Test Card"

- Initiates synchronization & data streams from the transmitter & recognizes them at receiver.

- Test memories at 120 MHz: 8-bit x 3 @ 40MHz.

- Captures the data at 120 MHz and compares, on the fly, w/data in a buffer on board.

- Stores received data & interrupts on error.

- Input Circuitry on Daughter Card

- Layout finished...ready for manufacture

- (see transp.)

- Test Circuitry on separate test card

- Daughter Cards also plug into this card

- Test Card is in layout

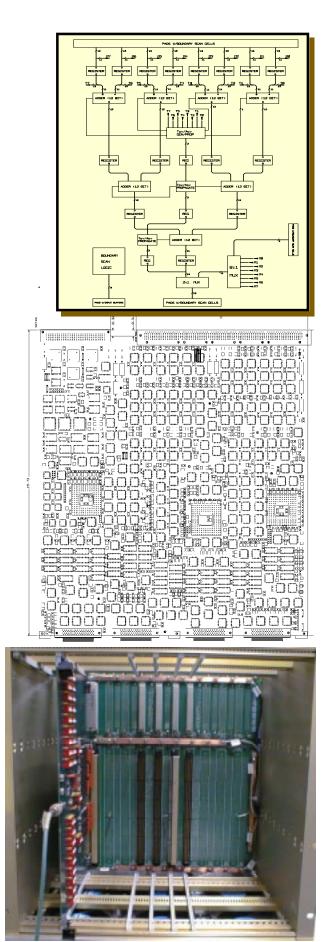

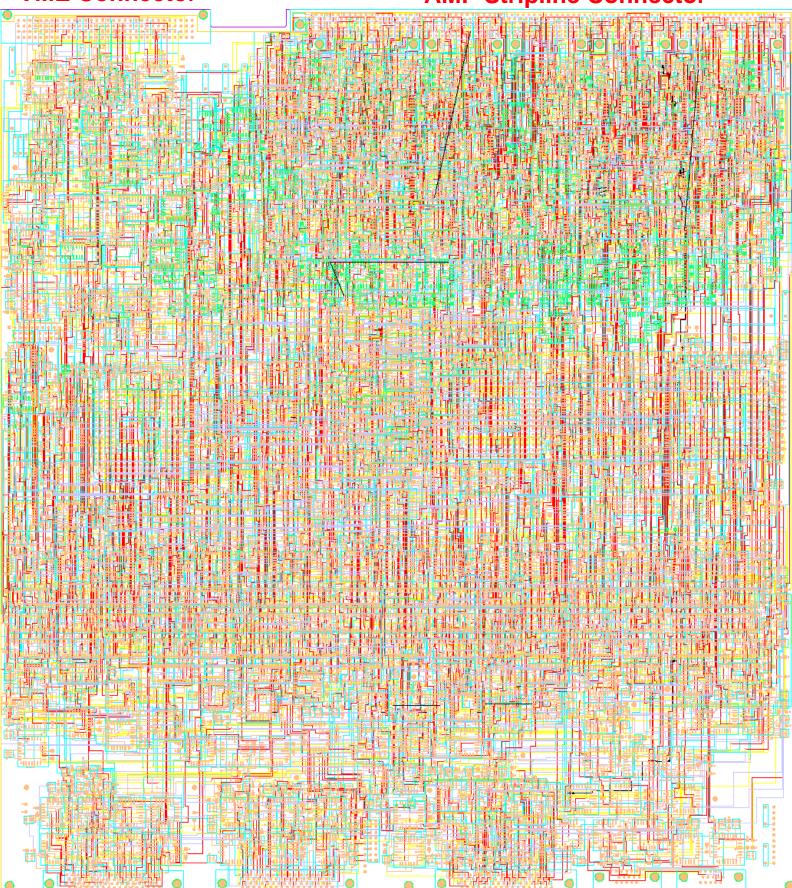

# **Receiver Card Layout**

#### **VME Connector**

#### **AMP Stripline Connector**

#### Inter-Crate Communication Connectors

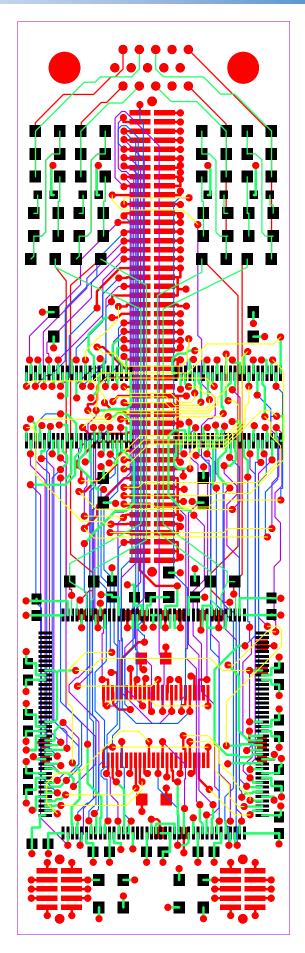

## **Receiver Daughter Card**

### **Layout Complete**

### Will hold for test card design and then submit both

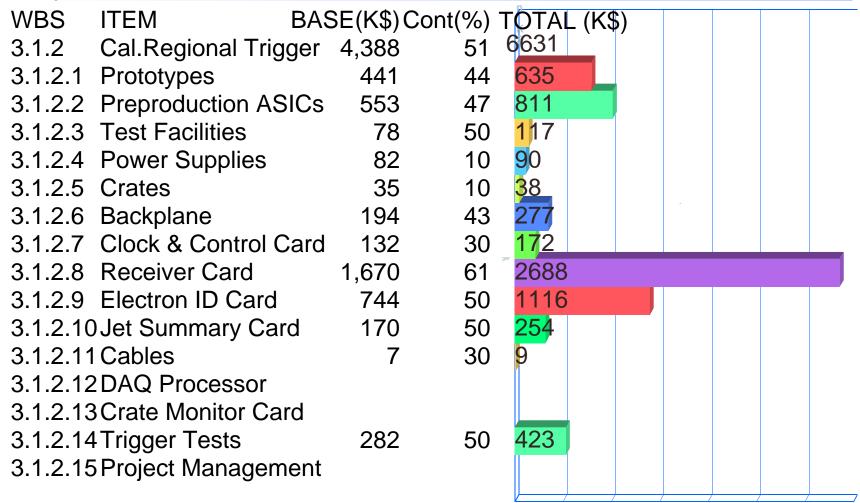

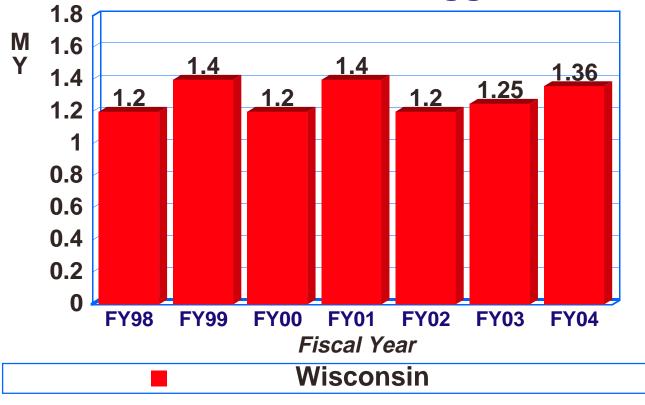

# **Calorimeter Trig. Costs at L4**

#### Changes since last May 1997 Review:

- Contingency analysis performed at lowest level (increased from 39->50%)

- Bottoms-up recosting & new WBS (no substantial net cost change)

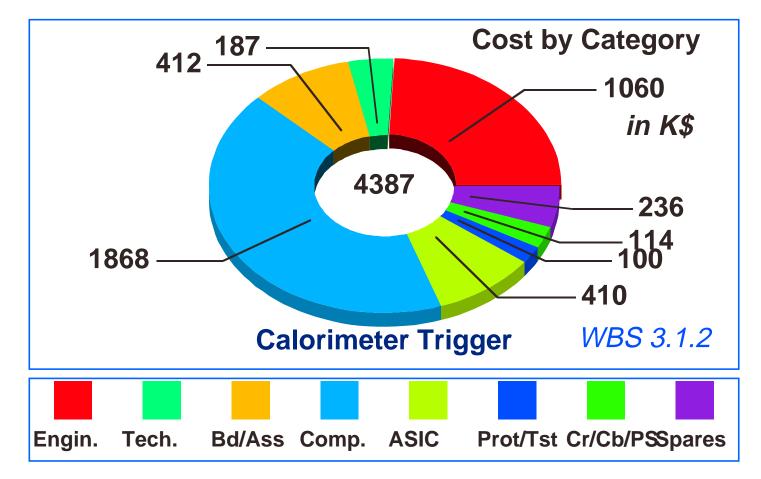

# Cost Drivers & Peak Engineering

#### Calorimeter Trigger WBS 3.1.2

Wesley Smith, U. Wisconsin

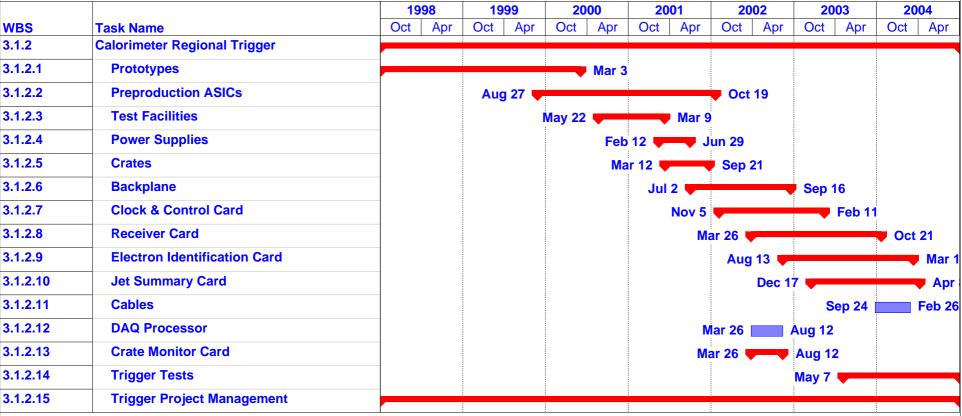

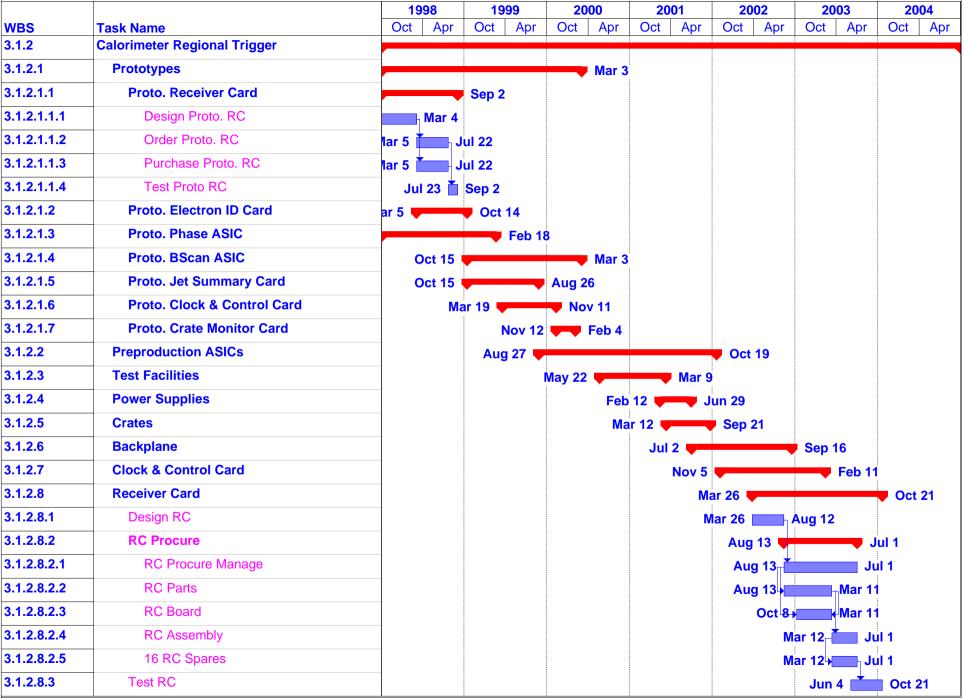

### Cal. Trig. Schedule & Milestones

| 1996     | _ 19    | 1997   |       | 1998         |       | 1999  |              | 2000   |        | 2001  |              | 2002   |            | 2003   |       | 2004  |     | 2005 |  |

|----------|---------|--------|-------|--------------|-------|-------|--------------|--------|--------|-------|--------------|--------|------------|--------|-------|-------|-----|------|--|

| Oct Ap   | r Oct   | Apr    | Oct   | Apr          | Oct   | Apr   | Oct          | Apr    | Oct    | Apr   | Oct          | Apr    | Oct        | Apr    | Oct   | Apr   | Oct | Apr  |  |

| Start P  | roto. B | ds. ┥  | Oc    | t 1          |       |       |              |        |        |       |              |        |            |        |       |       |     |      |  |

| Start AS |         | vel.   | Oc    | t 1          |       |       |              |        |        |       |              |        |            |        |       |       |     |      |  |

| Interi   | nal Des | sign F | Revie | w 1 🖣        | Oc    | :t 14 |              |        |        |       |              |        |            |        |       |       |     |      |  |

| F        | rototy  | pe Do  | esign | Finis        | shed  | • N   | <b>lay 2</b> | 7      |        |       |              |        |            |        |       |       |     |      |  |

|          | Int     | ernal  | Desi  | gn R         | eviev | v 2 ┥ | Sep          | 9      |        |       |              |        |            |        |       |       |     |      |  |

| F        | roto. E | Board  | s & 1 | <b>Fests</b> | Finis | shed  | N            | ov 11  | <br>   |       |              |        |            |        |       |       |     |      |  |

|          |         | Be     | gin A | SIC          | Prepi | roduc | ction        | ♦ N    | lay 19 | •     |              |        |            |        |       |       |     |      |  |

| -        |         | Be     | gin B | ackp         | lane  | & Cra | ate Pi       | roduc  | ction  | ♦ M   | lay 18       | 3      |            |        |       |       |     |      |  |

| -        |         |        |       | ASI          | C Dev | /elop | ment         | Con    | plete  | •     | Jun 2        | 9      |            |        |       |       |     |      |  |

|          |         |        |       |              | Fini  | sh A  | SIC F        | Prepro | oduct  | ion   | O            | ct 19  |            |        |       |       |     |      |  |

|          |         |        |       |              | Begi  | n Tri | gger         | Boar   | d Pro  | ducti | ion          | Ma     | r 25       |        |       |       |     |      |  |

|          |         |        |       |              |       |       | B            | egin   | ASIC   | Prod  | luctic       | on 🔶   | Aug        | 13     |       |       |     |      |  |

|          |         |        |       |              |       | С     | rate a       | & Bad  | ckpla  | ne Co | omple        | ete ┥  | Se         | o 16   |       |       |     |      |  |

|          |         |        |       |              |       |       | Begi         | n Pro  | duct   | ion B | oard         | Test   | <b>S</b> 🔶 | Jan 1  | 4     |       |     |      |  |

| -        |         |        |       |              |       |       |              |        |        | Des   | igns         | Finis  | hed        | ♦ M    | ay 6  |       |     |      |  |

|          |         |        |       |              |       |       |              |        |        | Finis | sh AS        |        | oduc       | tion   | N     | ov 18 |     |      |  |

| -        |         |        |       |              |       |       |              | F      | inish  | Trig  | ger E        | Board  | Proc       | ductio | on 🔶  | Feb   | 26  |      |  |

| 1        |         |        |       |              |       |       |              |        | Fin    | ish F | Produ        | ction  | Boa        | rd Te  | sts   | Ap    | r 8 |      |  |

| 1        |         |        |       |              |       |       |              |        |        | Be    | gin T        | rigge  | er Ins     | tallat | ion   | Ap    | r 9 |      |  |

|          |         |        |       |              |       |       |              |        |        | ٦     | <b>Frigg</b> | er Ins | talla      | tion F | inish | ed    | Se  | p 30 |  |

### Cal. Trig. Milest. & Integration

**Prototype Design Finished May '99 Proto. test w/ECAL Proto. Elect. Jun '99 Proto. Boards & Tests Finished Nov '99 Begin ASIC Preproduction May '00** Proto. test w/HCAL Proto. Elect. Jun '00 **Begin Backplane & Crate Production May '01 ASIC Development Complete Jun '01 Finish ASIC Preproduction Oct '01 Begin Trigger Board Production** Mar '02 **Begin Tests w/Final ECAL Elect.** Jul '02 **Begin ASIC Production Aug '02 Sep '02 Begin Tests w/Final HCAL Elect. Crate & Backplane Complete Sep '02 Begin Production Board Tests** Jan '03 **Designs Finished May '03 Finish ASIC Production Nov '03** Feb '04 **Finish Trigger Board Production Finish Production Board Tests Apr '04 Begin Trigger Installation Apr '04 Begin Final System tests w/E,HCAL** May '04 **Trigger Installation Finished** Sep '04

# New Cal. Trig. Milestones

### **Regional Trigger:**

- D220 Nov '98

- Review of Prototype Tests

- D250 Nov '98

- Review of Prototype Integration

- New Feb '99

- Test of Prototype Clock Board

- New Aug '99

- Delivery of Elec ID Pre-production ASIC

New Nov '99

- Delivery of Adder Pre-production ASIC

### **Global Trigger:**

- New Jul '98

- Prototype Sort ASIC Test Results

- Begin Fast Link tests

- New Nov '98

- Design Final Sort ASIC

- Choose Link Technology

- Finalize Processing Requirements

- New Nov '99

- Test Pre-production Sort ASIC

- Link Tests using final technology/pkg.

- Complete GCT Design

# 1998/9 Cal. Trigger Plans

## **Full dataflow tests**

- Receiver Card

- Backplane Prototype

- Pseudo Electron Isolation Card

- **Electron Isolation ASIC**

- Design in Vitesse GaAs

- Produce Prototype

- **Prototype Jet Summary Board**

- Trigger data summary generation

- Data transmission to global cal. trig. Intercrate data transfer

- Second crate & backplane

- Test transmit/align techniques

1st Test w/Trigger Primitive Logic Detailed Simulation

- Use full GEANT

- Check new calorimeter geometries

# Conclusions

# **CMS Regional Calorimeter Trigger**

### Receiver Card

- Cu copper serial receiver on daughter cards

- Use of Vitesse 7214 Receiver Chip

- Being Manufactured

- Receiver Daughter Card

- Layout finished

- New Test Card

- Will use daughter cards with dedicated test circuit

- In Layout

### • Plans

- Dataflow test with Receiver Card

- Data transmission test with daughter & test cards

- Cost & schedule

- Well developed