### Wesley Smith, *U. Wisconsin* CMS Trigger Project Manager

DOE/NSF Review April 12, 2000

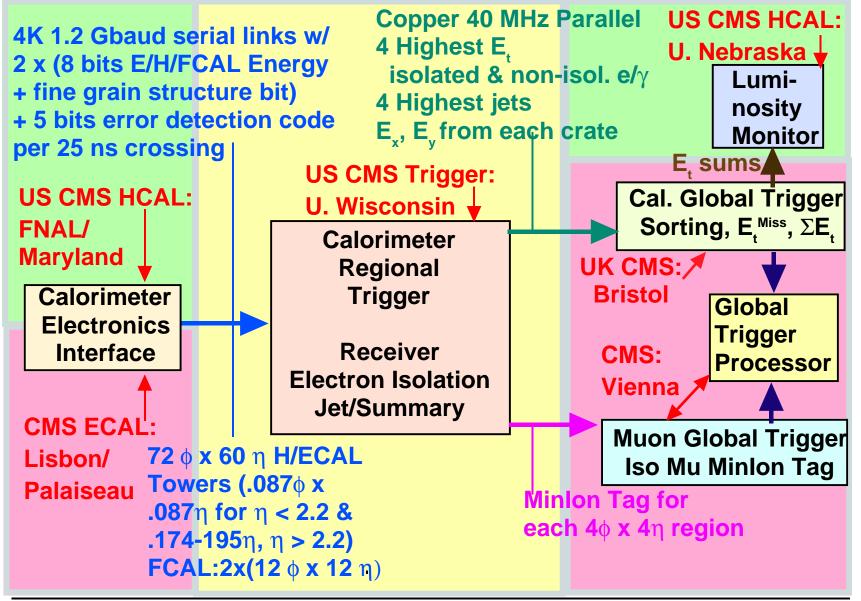

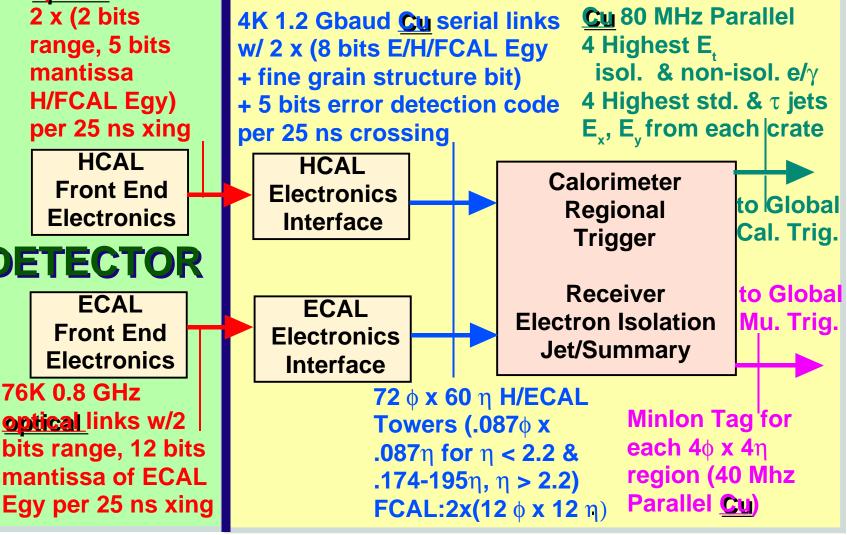

## **Calorimeter Trigger Overview**

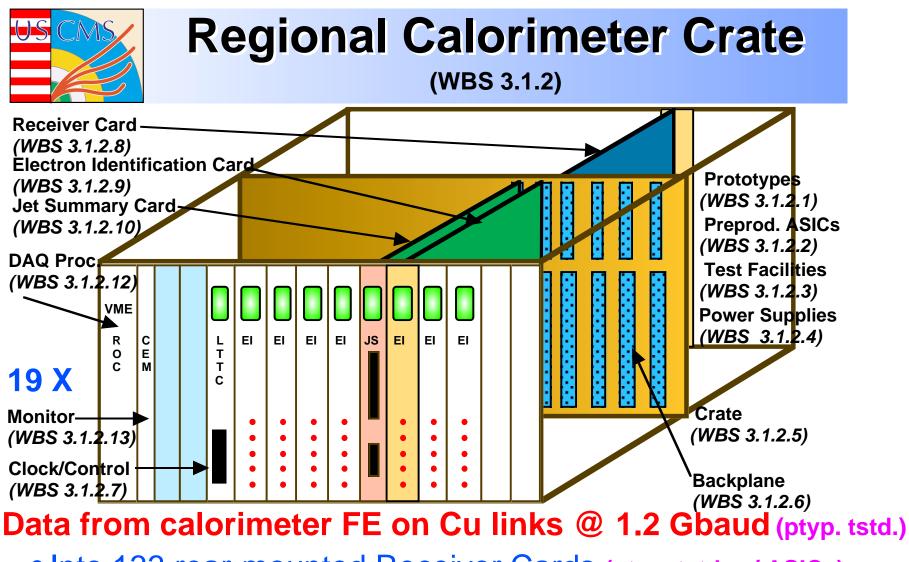

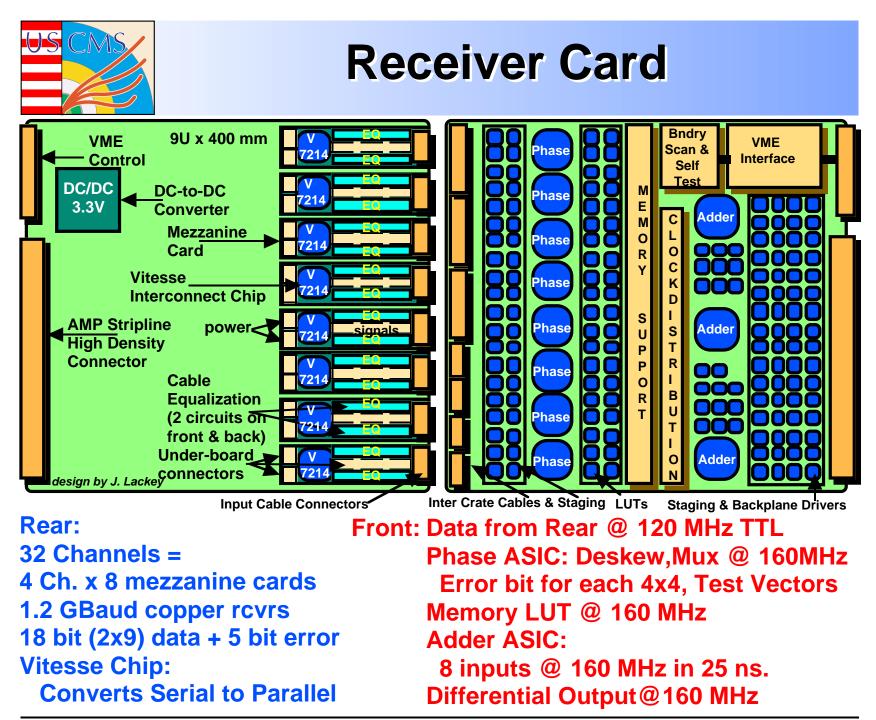

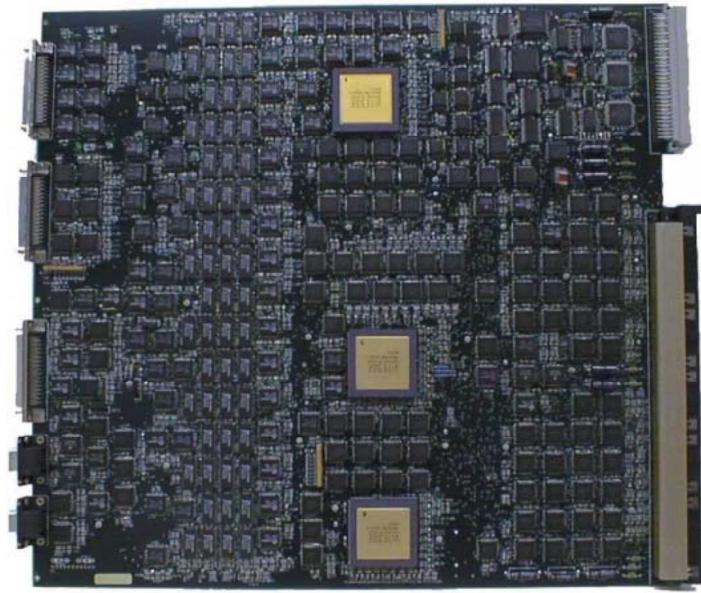

Into 133 rear-mounted Receiver Cards (ptyp. tstd. w/ ASICs)

160 MHz point to point backplane (ptyp. tstd.)

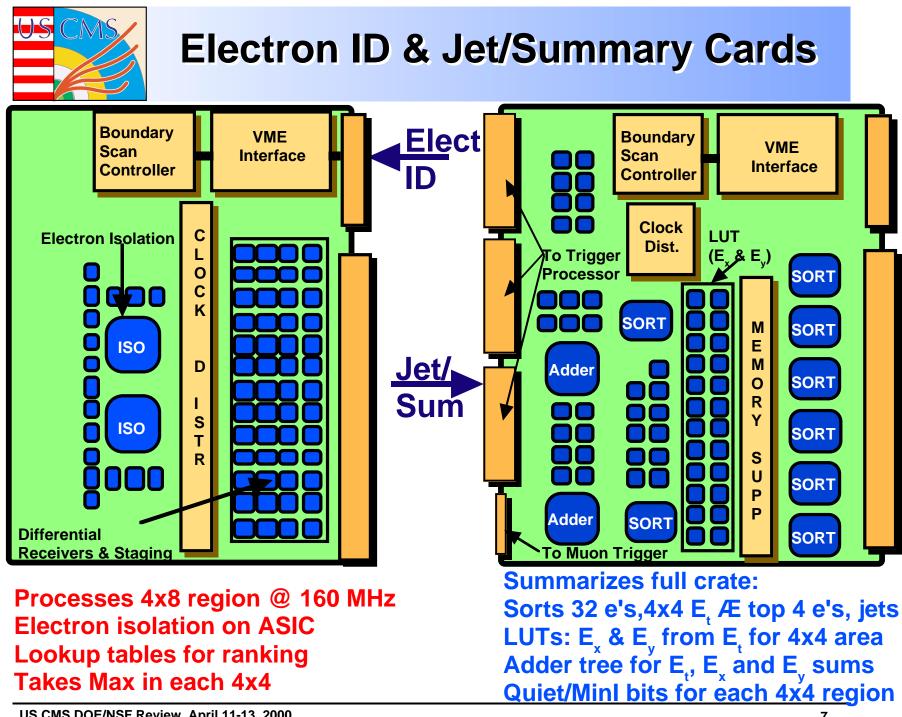

- 19 Clock&Control (ptyp. tstd.), 133 Electron ID (ptyp. tstd.)

- 19 Jet/Summary, Receiver Cards operate @ 160 MHz

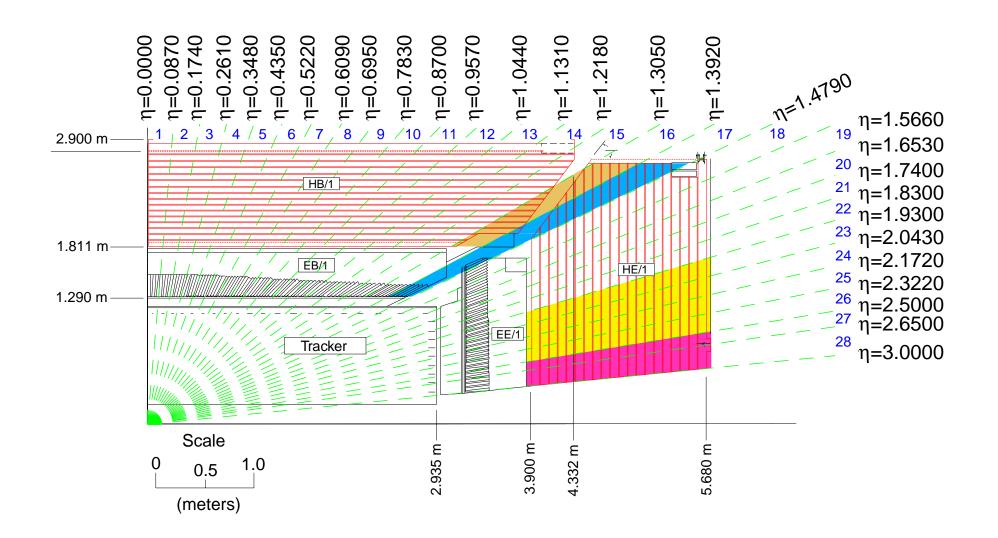

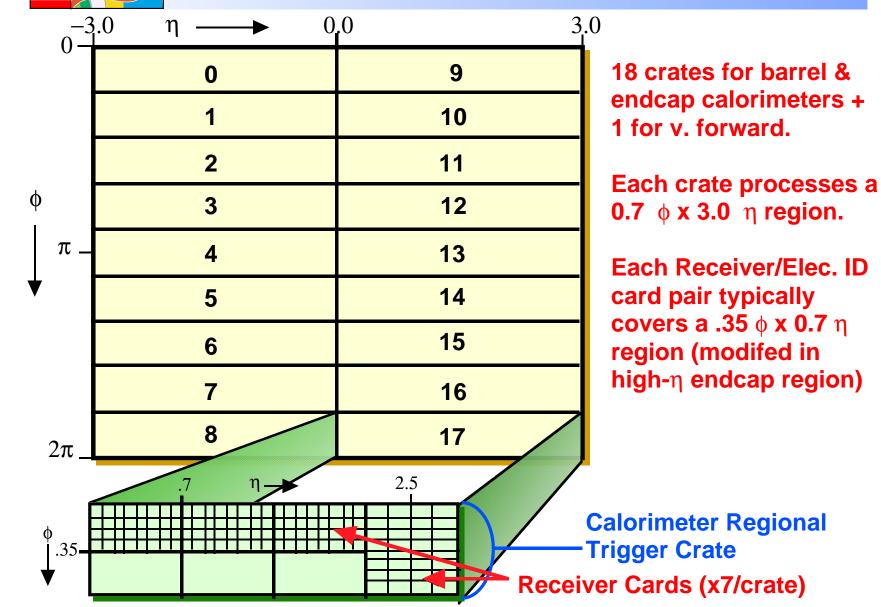

# Cal. Trigger Tower Mapping

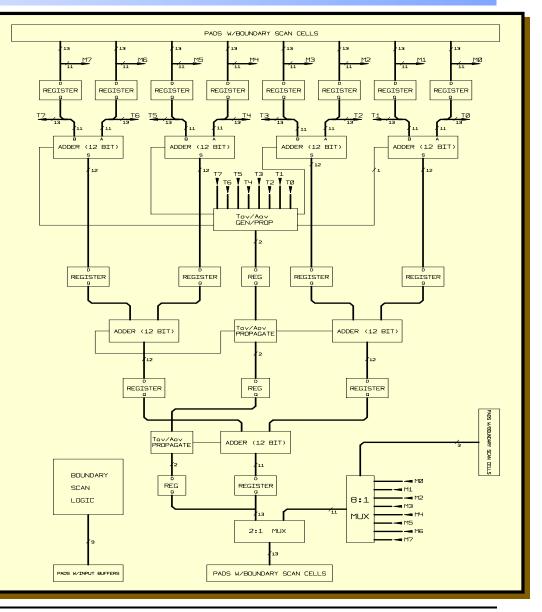

## 8 x 13-bit 160 MHz Adder ASIC

#### Vitesse 0.6µ H-GaAs Process: ECL I/O

- 13 bits per operand x 8 operands

- Thirteen bit output

- Latency:

25 ns @ 160 MHz

- Full Boundary Scan

- •~11,000 cells

- •4 Watts

- Tested > 200 MHz

- Operated on RC

- In Production

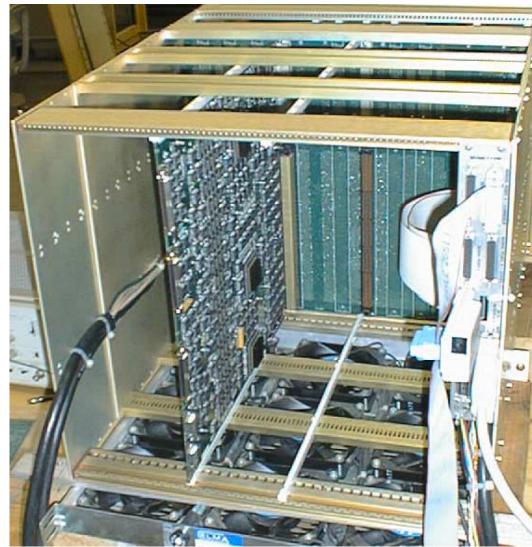

# **Cal. Trigger Dataflow Test**

**Prototype Crate with**

- 160 MHz Backplane

- Proto. Receiver Card (rear)

- Proto. Clock Card (front)

- Proto. Electron ID Card (front) Full 160 MHz dataflow verified

FRONT

REAR

## **Prototype Receiver Card**

160 MHz Prototype Receiver Card tests: • VME Interface checked

- Adder ASIC's checked

- Timing checked

- Intercrate sharing checked

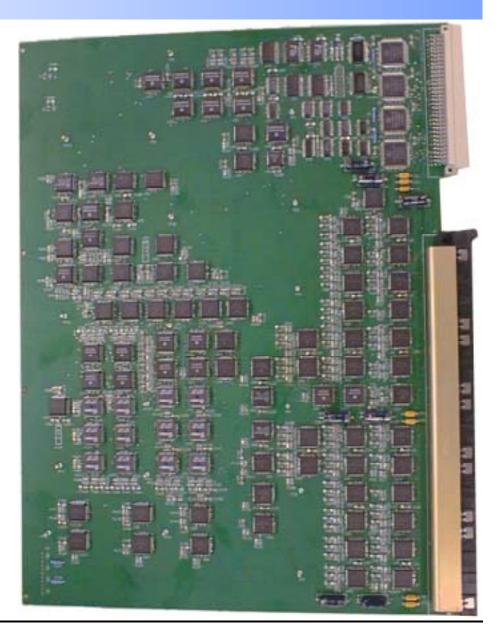

## **Electron ID Card Prototype**

## **Card tested:**

- VME Interface working

- Dataflow from Receiver Card through custom backplane works

- Timing checked

- Logic verified

# **ASIC Development - Receiver**

## **Prototype Phase ASIC (Receiver Card)**

- Input: 120 MHz TTL data from Gbit Link Mezzanine Card

- Output: 160 MHz ECL data & error detection

- Status:

- Layout & simulation finished, test vectors developed

- Vitesse design reviews passed, ready for manufacture

## **Prototype Boundary Scan ASIC (Receiver Card)**

- Boundary scan of Receiver Card Input

- Backplane drivers -- compact circuitry

- Status:

- Layout & simulation finished, test vectors developed

Vitesse design reviews passed, ready for manufacture

Will test with new Receiver Card prototype

# **ASIC Development - EID & JS**

**Electron ID ASIC (Electron ID Card)**

- Implements Electron Isolation algorithm

- Described in talk of S. Dasu

- Status: planned for completion by end of summer

- Design & Schematics Finished

- Layout & simulation next

- Sort ASIC (EID & Jet/Summary Card)

- Integrated backplane receivers & sorting

- Passes 4 highest rank of 32 inputs

- Sorts input before passing unto card

- Status: planned for completion by end of summer

- Design & Schematics Finished

- Layout & simulation next

- Will test with new Electron ID Card prototype

# **Calorimeter Trigger Links**

5.5K 0.8 GHz optical links w/ 2 x (2 bits range, 5 bits mantissa H/FCAL Egy) per 25 ns xing HCAL **Front End** Electronics

**Front End Electronics** 76K 0.8 GHz optical links w/2 bits range, 12 bits mantissa of ECAL

## **COUNTING ROOM**

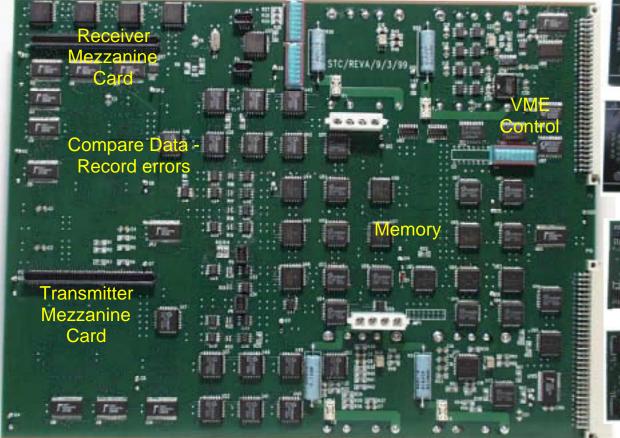

### **Copper Cable Gbit Serial Data Tests**

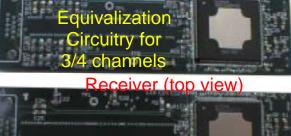

Serial Link Test Card includes VME, memories & comparison circuitry to fully test serial links @ 120 MHz TTL from Mezzanine Cards. (U. Wisconsin) Transmitter (bottom view) Mezzanine Transmit & Receive Cards convert 4 x 1Gb/s links to 120 MHz TTL w/ Vitesse 7214 & cable equalization

US CMS DOE/NSF Review, April 11-13, 2000

# **GBit Data Transmission**

Tests over 20 m Tek Stop: 5.00GS/s 3790 Acqs copper cable • PRELIMINARY! Vitesse 7214 4 x Gigabit Interconnect chip • twisted pair cables (Belden 9182 (150 ohm, 22AWG, foamed dielectric,twinax) grouped by fours & terminated with 8-pin DIN style connectors \$318 per 500 foot spool (\$2.10 per meter). 200mV 200ps Ax1 M 26

## **Trigger Link Bit Error Detection**

| Link error code simulation:                            | Bits with errors | Number of<br>Patterns | Percent of<br>Errors not<br>found |

|--------------------------------------------------------|------------------|-----------------------|-----------------------------------|

| • Between ECAL & HCAL Upper Lev                        | vel              |                       |                                   |

|                                                        | 0                | 1                     | 0.00                              |

| Readout & Cal. Regional Trigger                        | 1                | 24<br>276             | 0.00<br>0.00                      |

| • 2x(8 bits $E_{\tau}$ + 1 bit finegrain)              | 2                | 2024                  | 3.45                              |

|                                                        | 4                | 10626                 | 3.49                              |

| + 5 bits error detection code*                         | 5                | 42504                 | 3.03                              |

| 1 hit "Con Floa" - 21 hito/25 no                       | 6                | 134596                | 0.08                              |

| + 1 bit "Gap Flag" = 24 bits/25 ns                     |                  | 346104                | 0.17                              |

| <ul> <li>Full 5-bit Hamming Code* finds a</li> </ul>   | 8                | 735471                | 0.06                              |

| • Full 5-bit Hamming Code milds a                      |                  | 1307504               | 0.14                              |

| 1 & 2-bit errors (most common)                         | 10<br>11         | 1961256<br>2496144    | 0.01<br>0.01                      |

|                                                        | 12               | 2704156               | 0.01                              |

| <ul> <li>Also finds more than 96% of any</li> </ul>    | 13               | 2496144               | 0.02                              |

|                                                        | 14               | 1961256               | 0.10                              |

| other error type                                       | 15               | 1307504               | 0.15                              |

| · Dresedure unen errer is te zere er                   | 16               | 735471                | 0.06                              |

| <ul> <li>Procedure upon error is to zero ar</li> </ul> | 10 17            | 346104                | 0.30                              |

| log the error for readout by DAQ                       | 18               | 134596                | 0.08                              |

| log the error for readout by DAQ                       | 19               | 42504                 | 3.24                              |

| <ul> <li>Full implementation in Phase ASIC</li> </ul>  | 20               | 10626                 | 3.23                              |

| • I dif implementation in Thase Aon                    | 21               | 2024                  | 2.77                              |

| <ul> <li>Passed Vitesse Design Review.</li> </ul>      | 22               | 276                   | 0.03                              |

|                                                        | 23               | 24                    | 0.00                              |

|                                                        | 24               | 1                     | 0.00                              |

## **Plans for Next Year**

#### **ASIC Development**

#### • Boundary Scan & Phase ASIC

- Test prototype run from Vitesse

- Sort & Electron ID ASIC

- Finish layout & simulation

- Vitesse to manufacture, then test

#### **Next generation prototypes**

- Backplane

- Designed for final algorithms

- Receiver Card

- Used for testing Phase & Boundary Scan ASICs

- Will be fit with Gbit link mezzanine cards

- Electron Isolation Card

- Used for testing Sort & Electron ID ASICs

#### Serial Link Tests

- Select final cable

- Integrate new generation Vitesse link chip (7216)

- provide test boards for integration with HCAL, ECAL

### **Cal Trigger Schedule & Milestones**

|                           | 1995 1996                        |     |   |       | 1997 1998 |       |                  |        | 1999 2000 |       |            | 2001   |        | 2002          |       | 2003   |       | 2004  |                    |       |

|---------------------------|----------------------------------|-----|---|-------|-----------|-------|------------------|--------|-----------|-------|------------|--------|--------|---------------|-------|--------|-------|-------|--------------------|-------|

|                           |                                  | Apr |   | Apr   |           | Apr   |                  | 1      |           | Apr   |            | Apr    |        | Apr           |       | Apr    | Oct   |       | Oct                |       |

| -                         |                                  | •   |   |       |           | -     | 10/ <sup>·</sup> | •      |           | 1 1 1 |            | 1 1 1  |        | 1 1 1         | 000   | ''P'   | 000   | ''P'  | 000                | יץי י |

|                           |                                  |     |   |       |           |       |                  |        |           |       |            |        |        |               |       |        |       |       |                    |       |

|                           | Begin ASIC Development ♠ 10/1/97 |     |   |       |           |       |                  |        |           |       |            |        |        |               |       |        |       |       |                    |       |

| Advance A                 | SIC                              |     | I | ntern | al De     | esign | Revi             | ew 1   | ◆11       | /12/9 | 8          |        |        |               |       |        |       |       |                    |       |

| production                | on                               |     |   |       | Pro       | totyp | e Des            | sign   | Finis     | ned 🜢 | 9/9/       | 99     |        |               |       |        |       |       |                    |       |

| order to put              | t all                            |     |   |       |           |       |                  | -      |           | •     |            | /4/99  |        |               |       |        |       |       |                    |       |

| under conti               | act                              |     |   |       |           |       |                  | -      |           | Γ     |            |        |        |               |       |        |       |       |                    |       |

| with comm                 | tted                             |     |   |       | Be        | gin A | SIC              | Prep   | oduc      | tion  | <b>9/3</b> | 0/99   |        |               |       |        |       |       |                    |       |

| delivery                  |                                  |     |   | ->    |           |       | Pro              | oto. I | Board     | s &   | Tests      | Finis  | hed (  | <b>€_</b> 4/6 | /01   |        |       |       |                    |       |

| schedule                  |                                  |     |   |       |           |       | Revi             | ew t   | ests o    | of Re | giona      | l Trig | gger   | • 4/6         | /01   |        |       |       |                    |       |

| reduces                   |                                  |     |   |       | Pov       | iow   |                  |        | :         |       |            | ter tr |        | ·             | 1     | I      |       |       |                    |       |

| vendor/pro                | cess                             |     |   |       | Rev       | iew o |                  |        |           |       |            |        |        |               |       |        |       |       |                    |       |

| risk                      |                                  |     |   |       |           |       | Beg              | in Ba  | ickpla    | ne &  |            | e Pro  | oduct  | ion 🔶         | 8/31  | /01    |       |       |                    |       |

| Deless                    |                                  |     |   |       |           |       |                  |        | ASIC      | Deve  | lopm       | ent (  | Comp   | lete (        | 9/2   | 5/01   |       |       |                    |       |

| Delay                     |                                  |     |   |       |           |       |                  |        |           | Finis | h AS       | IC PI  | repro  | ducti         | on 🄶  | 1/30/  | 02    |       |                    |       |

| Jet/Summa                 | -                                |     |   |       |           |       |                  | D      |           |       |            | ard    | 1      |               | •     |        |       |       |                    |       |

| Proto. Boar               | a                                |     |   |       |           |       |                  | D      | gin       |       |            |        |        |               |       |        |       |       |                    |       |

| since not<br>essential fo | -                                |     |   |       |           |       |                  |        |           | I     | Begin      | ASI    | C Pro  | oduct         | ion 🔶 | 2/28   | /02   |       |                    |       |

| design                    |                                  |     |   |       |           |       |                  |        |           |       | Crate      | & Ba   | ackpl  | ane (         | Comp  | lete   | 9/18  | 8/02  |                    |       |

| validation.               |                                  |     |   |       |           |       |                  |        |           | В     | eain       | Produ  | uction | Boa           | rd Te | ests 4 | 9/18  | 3/02  |                    |       |

| Move J/S                  |                                  |     |   |       |           |       |                  |        |           |       | 3          |        |        |               |       | •      |       |       |                    |       |

| component                 |                                  |     |   |       |           |       |                  |        |           |       |            | D      | esigr  |               | nishe | •      |       |       |                    |       |

| tests to                  |                                  |     |   |       |           |       |                  |        |           |       |            |        |        | Finis         | sh As | SIC P  | Produ | ction | <mark>♦</mark> 10/ | 31/0  |

| Electron ID               |                                  |     |   |       |           |       |                  |        |           |       |            |        | Finis  | h Trig        | gger  | Board  | d Pro | ducti | on 🔶               | 2/10/ |

| Card.                     |                                  |     |   |       |           |       |                  |        |           |       |            |        | Fir    | nish I        | Produ | ction  | Boa   | rd Te | sts 🔺              | 3/9/  |

|                           |                                  |     |   |       |           |       |                  |        |           |       |            |        | • •    |               |       |        |       |       |                    | 5,51  |

# **Cal Trigger Personnel**

#### Physicists (at Wisconsin):

- Faculty: W. Smith & new hire

- Scientists: S. Dasu & P. Chumney (new)

**Engineers** (experienced team at Wisconsin):

- J. Lackey -- Lead Engineer & Designer

- Also Lead Engineer for Zeus Calorimeter Trigger

- M. Jaworski -- Board Layout & Design support

- Worked on Zeus Calorimeter Trigger

- H. Zhang -- ASIC Layout/Simulation (new)

- Worked on Zeus Calorimeter Trigger

- D. Wahl -- Copper Link Test/Development (new)

- PSL Engineer, assisted by lead PSL electronics engineer, P. Robl, who worked on Zeus Trigger

## Issues

### **Committee Concerns:**

- Increase Physicists & Engineering Personnel

- Done (see previous slide)

- Apply engineering resources to recover schedule

- Done: application to ASIC development & Gbit Link **Issue at time of last review:**

- Watch ASIC availability issues, as early procurement may become necessary.

- Entire ASIC production under contract with Vitesse

- Schedule rearranged to procure all of each ASIC immediately after successful test.

- Detailed series of reviews set up with Vitesse to provide strict QA/QC & testability

- Vitesse to deliver fully tested packaged ASICs

# Conclusions

## **Successful Prototyping Program**

- Crate, Backplane & Clock Card

- Receiver Card

- Electron Isolation Card

- Serial Link Test & Mezzanine Cards

- Adder ASIC -- now in production

### **Plans for next year**

- Completion of all first prototype & some second.

- Link prototypes used for integration w/ECAL,HCAL

**Cost & Schedule experience:**

- ASIC vendor/schedule accelerated

- Personnel augmented

- No use of contingency, on schedule