# **Trigger Report**

# Highlights, Milestones, Activities:

- Receiver Card Prototype delivered milestone

- Testing starts next week main activity

- Electron ID ASIC Package Study Completed

- Layout (floor plan) & timing studies

- 2 different Vitesse packages

#### • Electron ID Card Prototype Design & Layout close to completion

• Will construct after test of common design circuits used on Receiver Card

### **Near-term plans:**

- Full Dataflow tests

- Receiver Card Prototype

- Backplane Prototype

- Electron Identification Card Prototype

- Electron Isolation ASIC

- Design in Vitesse GaAs

- Produce Prototype

- Prototype Phase ASIC

- Design started

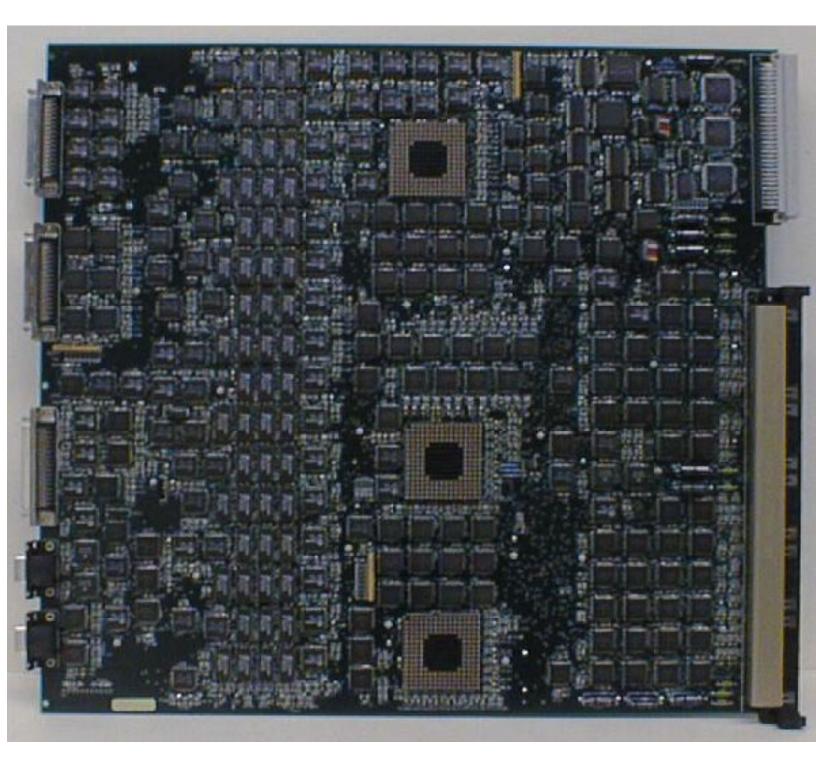

# **Receiver Card Prototype**

### **Prototype under test**

# **Muon Trigger**

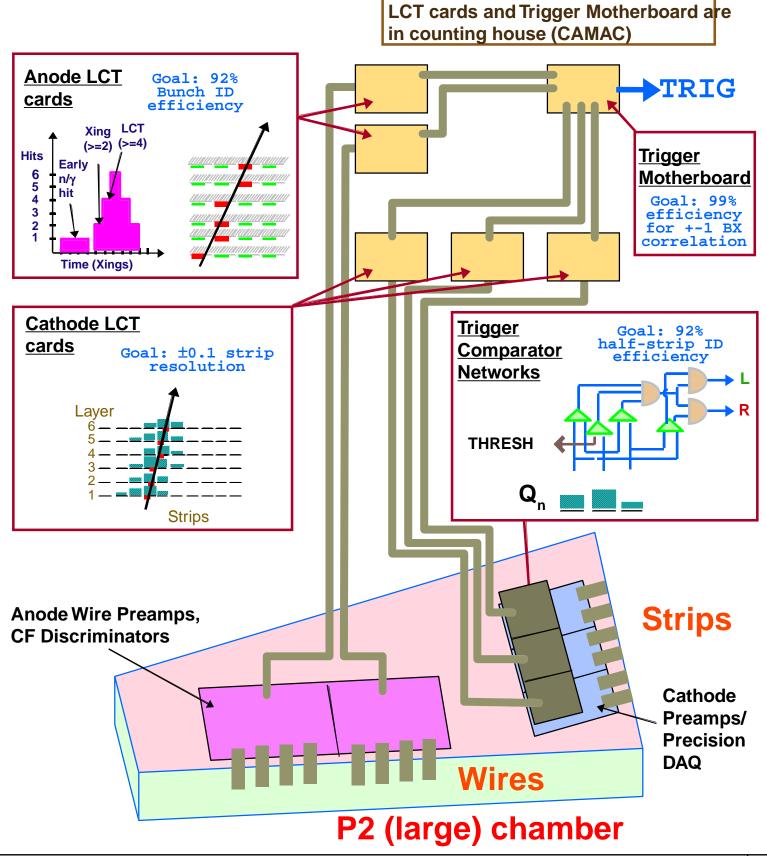

## **Highlights, Milestones, Activities:**

- Summer Beam Test: successful operation of

- Trigger Mother Board Prototype

- Cathode & Anode LCT Prototypes

#### Initial Designs & Documentation: - milestones

- Muon Port Card

- http://bonner-ntserver.rice.edu/cmscsctrigger

- Sector Receiver Card

- http://bonner-ntserver.rice.edu/motherboard/Archive/src.htm

- Sector Processor Cards

- http://www.phys.ufl.edu/~acosta/cms/trigger.html

#### • Design & Status Review at Rice

- Sep 27,28

- Good Progress on all fronts

- Revision to Muon Port Cards: RPC Input

- Movement of Electronics to Periphery

- Revision to Track-Finder

### **Near-term planned activities**

- Preparations for Summer '99 Test

- Designs of Prototype MPC, RC, SP

### **Summer '98 CERN Beam Tests**

- Data path: ME1/3  $\rightarrow$  DT T-F

- special link from ME1/3 motherboard, or from Sector Receiver card.

- No modification to DT T-F hardware

- ME1/3 becomes MB4 neighbor in  $\eta$

- inputs already there

- P<sub>T</sub> measurement determined mostly from MB1/MB2 which are barrel chambers

- Simplifies CSC T-F:

- Reduced Sector Processor logic and I/O

- Reduced I/O for Sector Receiver cards (no fan-out)

- Fewer CSC muons to sort

- No CSC crate interconnections

- Saves CSC latency

- Data path: MB1+MB2  $\rightarrow$  CSC T-F

- special DT Sector Receiver card

- CSC Trigger Motherboard design unchanged

- Uses  $\eta$  information for  $P_T$  determination

- B-field changes by  $\pm 5\%$

- Full 3D Track-Finding in  $\eta$  and  $\phi$

- reduces fakes

- Greater redundancy with ME2 in case ME1/3 misses hit

In any case, we can do track-finding in the overlap region with just the CSC chambers. Only lose  $P_T$  resolution without MB1 and MB2.

# Concerns

### **Calorimeter Trigger**

### HCAL Primitive Generation

- Can FE make tower sums?

- Geometry

- Can we find a good endcap tower geometry?

#### Design Complexity

- Long vendor turn-around

- Much vendor communication required

#### Integration

- System clocking

- Interfaces with ECAL/HCAL/Global CAL

## Muon Trigger

- Electronics on Periphery

- Is there room for the crates?

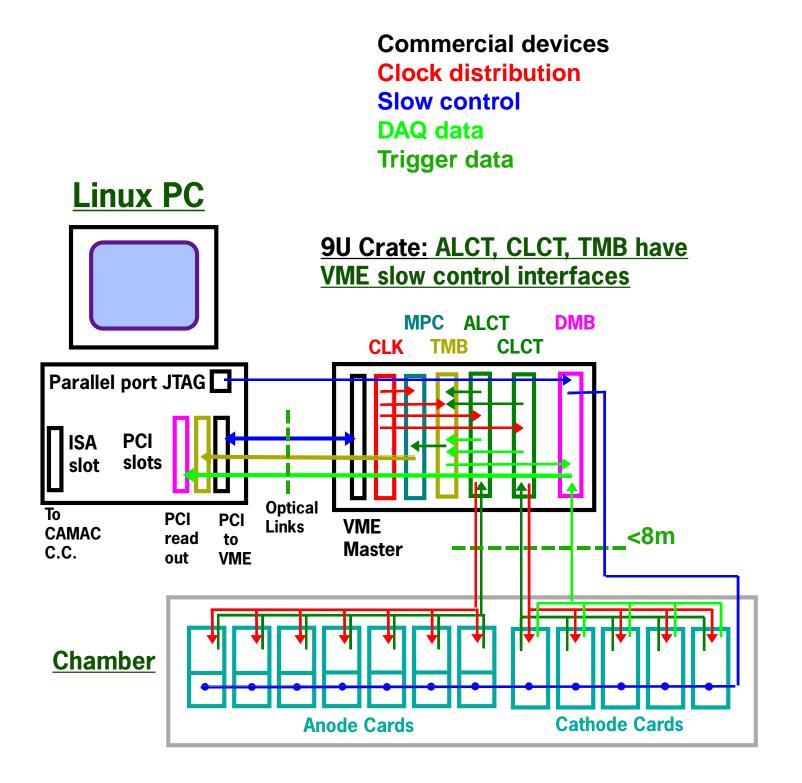

#### $\bullet$ Data flow design: MPC $\rightarrow$ SR $\rightarrow$ SP

Need details of processing, particularly in Sector Receiver, to proceed with Card Designs

• New effort underway for exact bit accounting

### • Interface with Russian Groups on ME1/1

#### Integration

• DAQ, Front End, & Slow Control Interfaces