### 402.2.6.3 Calorimeter Trigger Cost and Schedule

### Wesley H. Smith, U. Wisconsin HL LHC CMS Detector Upgrade Director's CD-1 Review April 4<sup>th</sup>, 2018

- Cost and Schedule

- Calorimeter Trigger Organizational aspects

- Contributing Institutions

- Optimization

- ES&H

- QA/QC

- Summary

Wesley Smith HL-LHC CD-1 Director's Review Trigger Cost and Schedule

Trigger L3 - Calorimeter

4/4/18

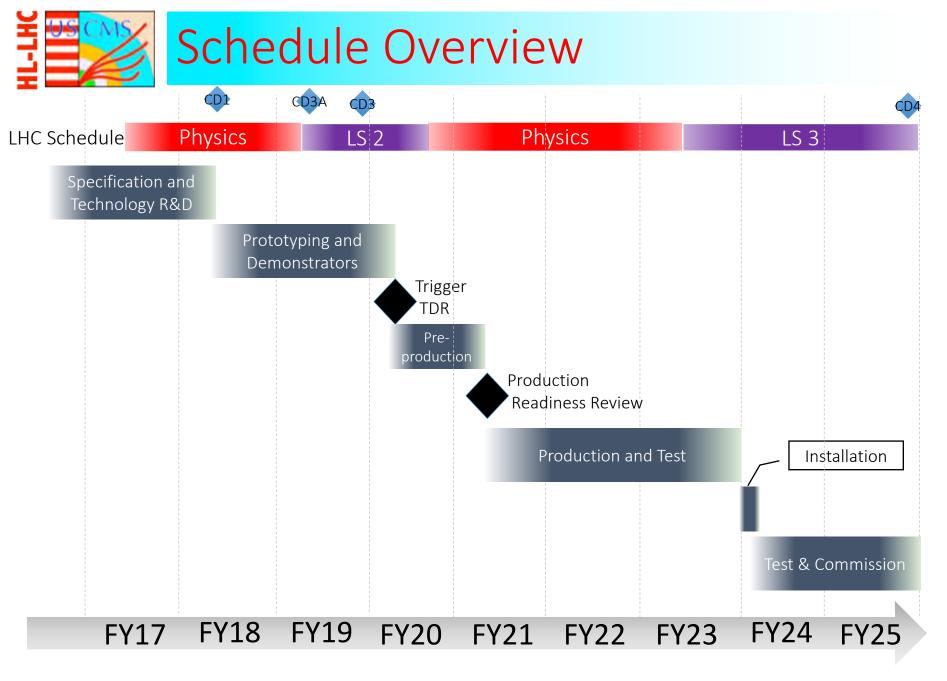

- Schedule Basis

- Phase-1 Construction and Installation schedule experience

- Next slides

- R&D program concludes with subsystem interconnect test at the end of CY19:

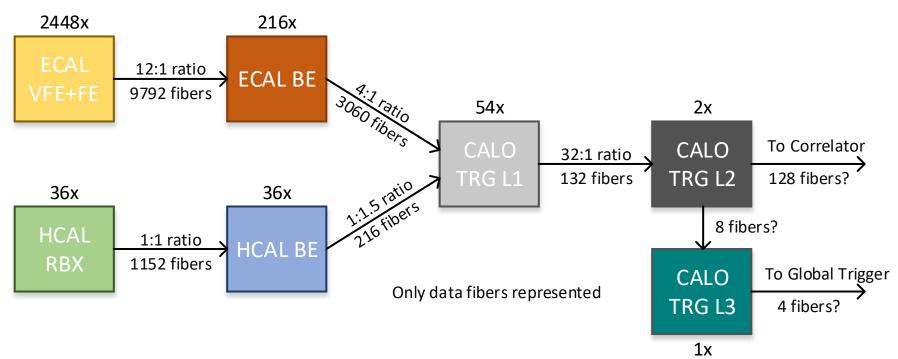

- Calorimeter  $BE \rightarrow Calorimeter Trigger \rightarrow Correlator$

- Test provides input for Trigger TDR

- Pre-production testing concludes at end of CY20

- Production starts with a pilot run of a few cards with card tests complete by end of CY21

- CY22 uses pilot and pre-production cards for final system integration tests

- Full production starts with funding for parts procurement at beginning of CY23

- Production testing complete and system shipped by end of CY23

- Testing, installation and integration at CERN in FY24

# **Construction Schedule Planning**

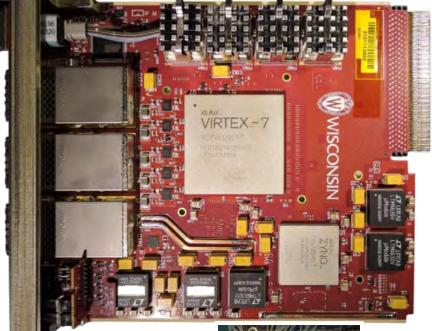

- Input: U. Wisc. CTP 7 MicroTCA Card for Phase 1 Cal. Trig.

- 12 MGT MicroTCA backplane links

- 67 Rx and 48 Tx 10G optical links

- Virtex-7 690T FPGA

- Data Processor

- ZYNQ `045 System-on-Chip (SoC)

- embedded Linux control platform

- Phase 1 Production Experience:

- Ist Proto: Q4/CY13

- 6 Pre. Prod. Proto: Q2-3/CY14

- Ist Production Board: Q1/CY15

- 50 Board Production Complete Q2CY15

- Installation Complete: Q2/CY15

- Commissioned, Operations start: Q3/CY15

- Layer-1 Calorimeter Trigger since 2016

- $\Rightarrow$  21 Months: 1st prototype to pp operations

- On schedule and on budget (performance in backup)

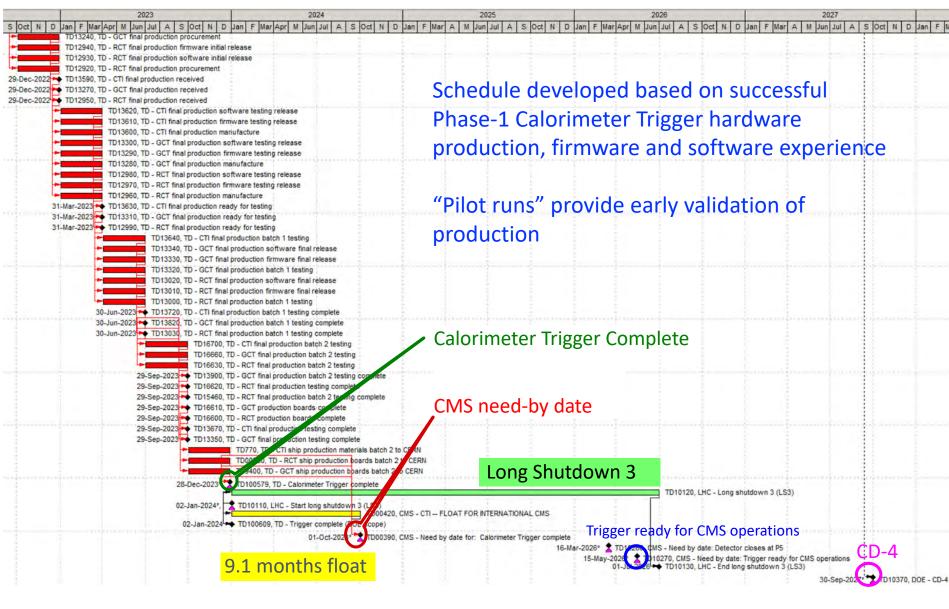

# **Construction Schedule Milestones**

### • FY21

- 2020Q4 preproduction test

- 2021Q1 final production design optimization

- 2021Q2 pilot production procure

- 2021Q3 pilot production manufacture

### • FY22

- 2021Q4 pilot test

- 2022Q1 system integration assembly

- 2022Q2 system integration test

# 2022Q3 system integration test

### FY23

- 2022Q4 final procurement

- 2023Q1 final manufacture

- 2023Q2 final test batch 1

- 2023Q3 final test batch 2, ship batch 1

### • FY24

- 2023Q4 ship batch 2

- 2024Q1-Q3 installation and integration at P5

### None

- Since calorimeter trigger has full self-test capabilities, both threshold and objective KPP are satisfied w/o requiring connected inputs or outputs.

- Trigger electronics can store up sequences of test patterns and inject them into the front end of the trigger electronics at speed

- Trigger electronics can receive its output, process and record this at speed for subsequent readout by DAQ.

### **Critical Path and Float**

Charge #2

4/4/18

TD10370, DOE - CD-4

# CMS-doc-13215

| Direct M&S<br>(\$) | Labor<br>(Hours)                                                                                                  | Direct + Indirect +<br>Esc. (\$)                                                                                          | Estimate<br>Uncertainty (\$)                                                                                                                                                                                      | Total Cost (\$)                                                                                                                                                                                                                                                                                        |

|--------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$3,603,594        | 75055                                                                                                             | \$8,306,257                                                                                                               | \$2,537,856                                                                                                                                                                                                       | \$10,844,113                                                                                                                                                                                                                                                                                           |

| \$162,000          | 26133                                                                                                             | \$213,104                                                                                                                 | \$21,310                                                                                                                                                                                                          | \$234,414                                                                                                                                                                                                                                                                                              |

| \$1,397,155        | 20444                                                                                                             | \$3,131,057                                                                                                               | \$867,194                                                                                                                                                                                                         | \$3,998,251                                                                                                                                                                                                                                                                                            |

| \$1,113,846        | 7550                                                                                                              | \$1,793,571                                                                                                               | \$526,309                                                                                                                                                                                                         | \$2,319,880                                                                                                                                                                                                                                                                                            |

| \$253,609          | 8669                                                                                                              | \$960,497                                                                                                                 | \$235,053                                                                                                                                                                                                         | \$1,195,550                                                                                                                                                                                                                                                                                            |

| \$29,700           | 4225                                                                                                              | \$376,989                                                                                                                 | \$105,832                                                                                                                                                                                                         | \$482,821                                                                                                                                                                                                                                                                                              |

| \$9,594            | 0                                                                                                                 | \$10,001                                                                                                                  | \$0                                                                                                                                                                                                               | \$10,001                                                                                                                                                                                                                                                                                               |

| \$1,266,845        | 28478                                                                                                             | \$4,011,483                                                                                                               | \$1,179,046                                                                                                                                                                                                       | \$5,190,529                                                                                                                                                                                                                                                                                            |

| \$768,000          | 0                                                                                                                 | \$940,612                                                                                                                 | \$470,306                                                                                                                                                                                                         | \$1,410,918                                                                                                                                                                                                                                                                                            |

|                    | (\$)<br>\$3,603,594<br>\$162,000<br>\$1,397,155<br>\$1,113,846<br>\$253,609<br>\$29,700<br>\$9,594<br>\$1,266,845 | (\$)(Hours)\$3,603,59475055\$162,00026133\$1,397,15520444\$1,113,8467550\$253,6098669\$29,7004225\$9,5940\$1,266,84528478 | (\$)(Hours)Esc. (\$)\$3,603,59475055\$8,306,257\$162,00026133\$213,104\$1,397,15520444\$3,131,057\$1,113,8467550\$1,793,571\$253,6098669\$960,497\$29,7004225\$376,989\$9,5940\$10,001\$1,266,84528478\$4,011,483 | (\$)(Hours)Esc. (\$)Uncertainty (\$)\$3,603,59475055\$8,306,257\$2,537,856\$162,00026133\$213,104\$21,310\$1,397,15520444\$3,131,057\$867,194\$1,113,8467550\$1,793,571\$526,309\$253,6098669\$960,497\$235,053\$29,7004225\$376,989\$105,832\$9,5940\$10,001\$0\$1,266,84528478\$4,011,483\$1,179,046 |

# **Cost Drivers:** Calorimeter Trigger

| CMS Driver                                       | Labor<br>(FTE-years) | Labor<br>(M\$) | M&S<br>(M\$) | Labor +<br>M&S<br>(M\$) | Estimate<br>Uncertainty<br>(M\$) | Total<br>(M\$) |

|--------------------------------------------------|----------------------|----------------|--------------|-------------------------|----------------------------------|----------------|

| TD.3 - Calorimeter Trigger delivery (M&S)        | 0.0                  | 0.00           | 1.50         | 1.50                    | 0.45                             | 1.95           |

| TD.5 - Correlator Trigger firmware               | 8.0                  | 1.41           | 0.00         | 1.41                    | 0.42                             | 1.83           |

| TD.5 - Correlator Trigger delivery (M&S)         | 0.0                  | 0.00           | 1.36         | 1.36                    | 0.41                             | 1.76           |

| TD.6 - Data Acquisition                          | 0.0                  | 0.00           | 0.94         | 0.94                    | 0.47                             | 1.41           |

| TD.3 - Calorimeter Trigger delivery (labor)      | 5.5                  | 0.89           | 0.08         | 0.97                    | 0.24                             | 1.22           |

| TD.5 - Correlator Trigger delivery (labor)       | 5.2                  | 0.80           | 0.06         | 0.85                    | 0.25                             | 1.10           |

| TD.3 - Calorimeter Trigger firmware and software | 6.0                  | 0.61           | 0.00         | 0.61                    | 0.17                             | 0.78           |

| TD.5 - Correlator Trigger software               | 2.9                  | 0.33           | 0.00         | 0.33                    | 0.10                             | 0.42           |

| TD.2 - Travel                                    | 0.0                  | 0.00           | 0.33         | 0.33                    | 0.03                             | 0.36           |

| TD.4 - Muon Track Finder R&D                     | 0.0                  | 0.00           | 0.01         | 0.01                    | 0.00                             | 0.01           |

RCT: 48 Total: 36 production boards, 4 test stand boards, and 6 spare boards.

- 2 pre-production boards repurposed for a third test stand.

- Estimated number of boards assumes 16 bits of trigger primitive data from each calorimeter cell being processed by the trigger processor boards. These boards have 96 16-Gbit input links, running 352 bits at 40 MHz. The total number of 70.4K channels is composed from 61.2K actual EB channels and 9.2K actual HB channels.

- GCT: 3 production boards and 1 spare board.

- Number of boards is based on processing RCT output

- Cost per board: \$21.19K

- Prototype and Pre-production cost: \$22.94K

- Detail on next slide

# **Details of APT Cost** – BoE: cmsdoc-13102

| Primary Item      | Subitem                          | Ext. Cost | Qty   | Unit Cost  | Comments                                                                           |

|-------------------|----------------------------------|-----------|-------|------------|------------------------------------------------------------------------------------|

| APT (Advanced     |                                  |           |       |            |                                                                                    |

| ProcessorTrigger) |                                  |           |       |            |                                                                                    |

| Fully Assembled   |                                  |           |       |            |                                                                                    |

| Board             |                                  | \$23,374  |       |            |                                                                                    |

|                   | PCB Fabrication                  | \$1,800   |       |            | 0 Ultra-low loss material used                                                     |

|                   | Heat Exchanger Assembly          | \$750     |       |            | 0 Custom design likely copper with embedded fans                                   |

|                   | Contract Assembly Solder Reflow  | \$900     |       |            |                                                                                    |

|                   | Power Subsystem Components       | \$420     |       |            | 048V input modules, secondary converters                                           |

|                   | Timing Subsystem Components      | \$120     |       |            | 0 Clock circuitry                                                                  |

|                   | Miscellaneous Components         | \$300     |       |            | OResistors, capacitors, connectors smaller ICs, etc.                               |

|                   | Panel Hardware                   | \$75      |       |            | 5 Hardware including panels and handles/ejectors                                   |

| (Prototype built) | Mezzanine: ELM                   | \$1,250   |       |            | 0ZYNQ-based, use Ultrascale+ family to reduce board unit cost                      |

| (Prototype built) | Mezzanine: IPMC                  | \$360     |       |            | 0 IPMI Controller for ATCA blades per the ATCA specification                       |

|                   | Mezzanine: PT LUT                |           | 0.0   | ວ \$2,430  | 0 Required for Corl Trigger                                                        |

|                   |                                  |           |       |            | Virtex device in C2104 Package for 100 active links. XCVU9P-1FLGC2104E             |

|                   |                                  |           |       |            | quantity: 3 and more, price: \$12774, XCVU9P-2FLGC2104E quantity: 3 and            |

|                   | Processing FPGA                  | \$12,774  | 4 1.0 | J \$17,78? | 3 more, price: \$17783; -2 device is costed.                                       |

|                   |                                  |           |       |            | Assuming either 12 RX or 12 TX @16G. Use present average 14G price. 16G            |

|                   | Optical Modules16G               | \$3,120   |       |            | 0 available soon                                                                   |

|                   | Optical Modules25G               |           | 0.0   |            | 5 assuming 1 device = 4TX+4RX                                                      |

|                   | RTM Board                        | \$1,505   |       | រ \$1,505  | 5 See itemization below                                                            |

|                   | Remove 1.9% for FY17 vs FY18     | \$22,938  | i i   |            | used for prototypes and preproduction                                              |

|                   | Remove following 2%/yr           |           |       |            |                                                                                    |

|                   | escalation rate                  | \$21,191  | 4     |            | used for pilot and final production                                                |

|                   |                                  |           |       |            |                                                                                    |

| RTM Optical Board |                                  | \$1,505   | ,     |            |                                                                                    |

|                   |                                  |           |       |            | Assumes ultra low loss dielectric, layer count sufficient for high quality routing |

|                   | PCB Fabrication                  | \$160     |       |            | Osolution between optical modules and RTM connector                                |

|                   | Contract Asssembly Solder Reflow |           |       |            |                                                                                    |

|                   | Interface logic (power, IPMI)    | \$85      | 5 1.0 | .0 \$85    |                                                                                    |

|                   |                                  |           |       |            | Assuming either 12 RX or 12 TX @16G. Use present average 14G price. 16G            |

|                   | Optical components               | \$1,040   |       |            | 0 available soon                                                                   |

|                   | Panel Hardware                   | \$75      | 5 1.0 | 0 \$75     | 5 Rear face panel                                                                  |

| 1                 | Misc electrical components       | \$45      | 5 1.0 | 0 \$45     | 5 Includes connector                                                               |

| 4                 |                                  |           |       |            |                                                                                    |

4/4/18

# **Calorimeter Trigger Labor Costs**

- Electronics Engineering and Technical work to design, produce, and test the calorimeter trigger electronics

- Software Engineering to produce the software to program, test, operate, diagnose, configure, validate and read out the calorimeter L1 trigger upgrade electronics.

- This includes software to interface with the Trigger Online System

- Firmware Engineering to implement the full functionality of the calorimeter L1 trigger upgrade electronics

- Including implementing the trigger algorithms, diagnostics, data acquisition and readout.

- SW and FW produced in validated releases for testing cards individually, integrated into a test system, integrated into the final test system, full production tests, and system installation and commissioning.

- All labor costs based on actual costs for corresponding tasks for the Phase 1 Trigger Upgrade

- In most cases by the same people

- Standardize within US CMS Trigger Project

- Use of a single FPGA family: Xilinx Ultrascale/+

- Also used across CMS upgrade and other CERN projects

- Allows negotiation of discounts through CERN and US distributor (Avnet) – as was done in Phase-1.

- Standardize across US CMS Upgrade Project

- Use of a common crate/backplane infrastructure

- Use same ATCA architecture as is being used by other CMS and ATLAS subsystems

- Built to similar specifications by common vendors.

- Opportunities for pooling spares and cooperation on engineering.

- This allows use of common components such as:

- Use of standard DAQ/Trigger/Clock Interface: DTH

- Common connection to CMS data acquisition, trigger timing and control systems.

- Developed by CMS CERN CDAQ group

### Explore alternative architectures (next slide)

### **Alternative Architecture Studies**

- Example: Use a smaller and less expensive FPGA (below)

- Fewer links per card → more cards, more layers (latency), awkward geometry, more complexity, more cost

- Example: Use two cheaper FPGAs per card

- Large usage of links and circuitry for data exchange, dividing logic leads to inefficiencies, complex clocking to synchronize, more cost

### Ratios reflect $\eta x \varphi$ input regions to output regions

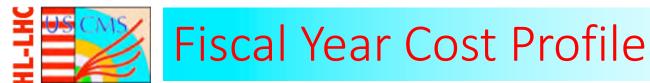

WBS 402.6.3 - TD - Calorimeter Trigger Base Budget= \$3,131,057 (AY\$)

Wesley Smith HL-LHC CD-1 Director's Review

Charge #2

# Maturity of Design

- ATCA hardware is similar to μTCA Phase-1 System

- Prototype Cards already made capture ATCA interface

- IPMC, ELM1: control interfaces, CDB: Ethernet and physical interfaces

- Phase-2 system is based on same classes of components as Phase-1

- Hardware, Firmware and Software based on experience of the same team that built and wrote hardware, software and firmware for Phase-1 trigger system

- Hardware is based upon common ATCA hardware platform also to be used by other CMS subsystems

- Same team wrote software and firmware for Phase-1 trigger system → scope and requirements well understood

- Requirements are detailed in Trigger Interim Document

- Schedule is designed based upon experience of Phase-1 system.

- Most M&S contingency set per OPSS rules at M4: 30%, since the same team has just built a similar technology µTCA calorimeter trigger for Phase 1 and the dominant costs (FPGAs, Optical components, memories) are based on quotes.

- Exception for travel, COLA and shipping at M2: 10%.

- Most Labor contingency set per OPSS rules at L4: 30% since the since the same team has just built a similar technology µTCA calorimeter trigger along with Firmware and Software for Phase 1 and the various labor activities are based on this experience.

- Experience with Phase 2 R&D and prototyping thus far bears this out.

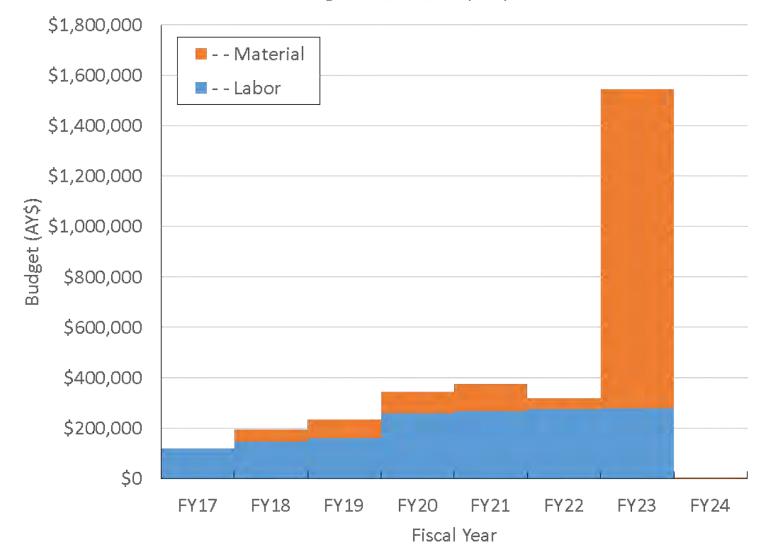

### Risk Register: CMS-doc-13480

| RI-ID          | Title                                                     | Probability | Cost Impact        | Schedule Impact | P * Impact (k\$) |

|----------------|-----------------------------------------------------------|-------------|--------------------|-----------------|------------------|

| Bisk Type : Th | nreat (5)                                                 |             |                    |                 |                  |

| RT-402-6-03-D  | TD - I/O performance does not<br>meet requirements (DOE)  | 20 %        | 250 500<br>750 k\$ | 3 5 7<br>months | 100              |

| RT-402-6-06-D  | TD - Baseline FPGA does not<br>satisfy requirements (DOE) | 20 %        | 126 252<br>504 k\$ | 1 3 6<br>months | 59               |

| RT-402-6-04-D  | TD - Additional board redesign<br>is required (DOE)       | 10 %        | 50 125<br>250 k\$  | 1 3 6<br>months | 14               |

| RT-402-6-02-D  | TD - Board or parts vendor non-<br>performance (DOE)      | 10 %        | 25 125<br>250 k\$  | 1 3 6<br>months | 13               |

| RT-402-6-05-D  | TD - Additional firmware<br>development is required (DOE) | 20 %        | 12 25 50<br>k\$    | 1 2 3<br>months | 6                |

### Probability-weighted Mean Cost Impact

### Managed Trigger Risks & Mitigation

Senior Engineer becomes unavailable (Low Risk)

- Hire new engineer, subcontract to consulting firm, use FNAL engineer

- Funding is delayed (Low Risk)

- Commission with prototypes and/or fewer production boards

- Software or Firmware does not meet requirements (Low Risk)

- Hire extra expert effort to recover schedule and help personnel

- Boards are delayed (design, manufacture or testing) (Low Risk)

- Hire extra effort to speed up testing schedule

- Vendor non-performance (Low Risk)

- Acquire spending authority to use alternative vendors (while original funds are being unencumbered).

- Input or output electronics (non-trigger) delayed (Low Risk)

- Built in capabilities of trigger electronics provide signals for their own inputs & outputs

### Risk Register CMS-doc-13480

### RT-402-6-02-D TD - Board or parts vendor non-performance (DOE)

| Risk Rank:            | 2 (Medium) Scores: Probability : 2 (L) ; Cost: 1 (L)<br>Schedule: 2 (M))                                                                                                                           | Risk Status:               | Open                                                                                                                              |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Summary:              | If the vendor has intermittent problems during the product parts from batch N do not meet electrical specs causing a sought. Similarly if there is significant vendor delay to during per L3 area. | delay of order one batch l | ength or another vendor is                                                                                                        |

| <b>Risk Type:</b>     | Threat                                                                                                                                                                                             | Owner:                     | Jeffrey W Berryhill                                                                                                               |

| WBS:                  | 402.6 TD - Trigger and DAQ                                                                                                                                                                         | Risk Area:                 | External Risk / Vendors                                                                                                           |

| Probability<br>(P):   | 10%                                                                                                                                                                                                | Technical<br>Impact:       | 2 (M) - significantly substandard                                                                                                 |

| Cost Impact:          | PDF= 3-point - triangularMinimum= 25 k\$Most likely= 125 k\$Maximum= 250 k\$Mean= 133 k\$P * <impact> = 13 k\$</impact>                                                                            | Schedule Impact:           | PDF= 3-point - triangularMinimum= 1 monthsMost likely= 3 monthsMaximum= 6 monthsMean= 3.33 monthsP* <impact>= 0.3 months</impact> |

| Basis of<br>Estimate: | Based on previous dealings with similar vendors. Another<br>Possible cost increases due to new vendor choice.                                                                                      | r production batch or ven  |                                                                                                                                   |

| Cause or<br>Trigger:  |                                                                                                                                                                                                    | Impacted<br>Activities:    | Procurement of production<br>electronics.The risk is repeated per L3<br>area.                                                     |

| Start date:           | 1-Jan-2021                                                                                                                                                                                         | End date:                  | 1-Jan-2024                                                                                                                        |

| Risk<br>Mitigations:  |                                                                                                                                                                                                    |                            |                                                                                                                                   |

| Risk<br>Responses:    | Diagnose the problem. If a simple technical fix is available                                                                                                                                       | e, consider reordering. If | not, find another vendor.                                                                                                         |

| More details:         |                                                                                                                                                                                                    |                            |                                                                                                                                   |

### RT-402-6-03-D TD - I/O performance does not meet requirements (DOE)

| Risk Rank:            | 2 (Medium) Scores: Probability : 2 (L) ; Cost: 2 (M)<br>Schedule: 3 (H))                                                 | Risk Status:            | Open                                                                                                                            |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Summary:              | I/O requirements of a trigger subsystem change                                                                           |                         |                                                                                                                                 |

| Risk Type:            | Threat                                                                                                                   | Owner:                  | Jeffrey W Berryhill                                                                                                             |

| WBS:                  | 402.6 TD - Trigger and DAQ                                                                                               | Risk Area:              | Technical Risk / Requirements                                                                                                   |

| Probability<br>(P):   | 20%                                                                                                                      | Technical<br>Impact:    | 2 (M) - significantly substandard                                                                                               |

| Cost Impact:          | PDF= 3-point - triangularMinimum= 250 k\$Most likely= 500 k\$Maximum= 750 k\$Mean= 500 k\$P * <impact>= 100 k\$</impact> | Schedule Impact:        | PDF= 3-point - triangularMinimum= 3 monthsMost likely= 5 monthsMaximum= 7 monthsMean= 5 monthsP * <impact>= 1.0 months</impact> |

| Basis of<br>Estimate: | 10-30% upscope of a 100-board production to meet chang batches.                                                          | ed requirements. Schedu | le delays due to the acquisition of more                                                                                        |

| Cause or<br>Trigger:  |                                                                                                                          | Impacted<br>Activities: | Production procurement, assembly,<br>and testing                                                                                |

| Start date:           | 1-Jan-2021                                                                                                               | End date:               | 1-Jan-2024                                                                                                                      |

| Risk<br>Mitigations:  |                                                                                                                          |                         |                                                                                                                                 |

| Risk                  |                                                                                                                          |                         |                                                                                                                                 |

| Responses:            |                                                                                                                          |                         |                                                                                                                                 |

| More details:         |                                                                                                                          |                         |                                                                                                                                 |

### RT-402-6-04-D TD - Additional board redesign is required (DOE)

| Risk Rank:            | 2 (Medium) Scores: Probability : 2 (L) ; Cost: 1 (L)<br>Schedule: 2 (M))                                               | Risk Status:              | Open                                                                                                                              |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Summary:              | A prototype or production batch has technical flaws.                                                                   |                           |                                                                                                                                   |

| Risk Type:            | Threat                                                                                                                 | Owner:                    | Jeffrey W Berryhill                                                                                                               |

| WBS:                  | 402.6 TD - Trigger and DAQ                                                                                             | Risk Area:                | Technical Risk / Reliability or<br>Performance                                                                                    |

| Probability           | 10%                                                                                                                    | Technical                 | 2 (M) - significantly substandard                                                                                                 |

| (P):                  |                                                                                                                        | Impact:                   |                                                                                                                                   |

| Cost Impact:          | PDF= 3-point - triangularMinimum= 50 k\$Most likely= 125 k\$Maximum= 250 k\$Mean= 142 k\$P * <impact>= 14 k\$</impact> | Schedule Impact:          | PDF= 3-point - triangularMinimum= 1 monthsMost likely= 3 monthsMaximum= 6 monthsMean= 3.33 monthsP* <impact>= 0.3 months</impact> |

| Basis of<br>Estimate: | 2-10 boards at 25k each are found to require a technical re<br>repeated per L3 area.                                   | edesign. 1-6 months for r | edesign and procurement. Risk is                                                                                                  |

| Cause or<br>Trigger:  |                                                                                                                        | Impacted<br>Activities:   | Design of next protoype/batch.                                                                                                    |

| Start date:           | 1-Jul-2017                                                                                                             | End date:                 | 1-Jan-2024                                                                                                                        |

| Risk<br>Mitigations:  |                                                                                                                        |                           |                                                                                                                                   |

| Risk                  |                                                                                                                        |                           |                                                                                                                                   |

| <b>Responses:</b>     |                                                                                                                        |                           |                                                                                                                                   |

| More details:         |                                                                                                                        |                           |                                                                                                                                   |

### RT-402-6-05-D TD - Additional firmware development is required (DOE)

| Risk Rank:            | 1 (Low) Scores: Probability : 2 (L) ; Cost: 1 (L) Schedule: 1 (L))                                                  | Risk Status:            | Open                                                                                                                           |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Summary:              | Firmware does not meet technical or scientific requirements a                                                       | t time of milestoned    | releases.                                                                                                                      |

| Risk Type:            | Threat                                                                                                              | Owner:                  | Jeffrey W Berryhill                                                                                                            |

| WBS:                  | 402.6 TD - Trigger and DAQ                                                                                          | Risk Area:              | Technical Risk / Reliability or<br>Performance                                                                                 |

| Probability           | 20%                                                                                                                 | Technical               | 1 (L) - somewhat substandard                                                                                                   |

| (P):                  |                                                                                                                     | Impact:                 |                                                                                                                                |

| Cost Impact:          | PDF= 3-point - triangularMinimum= 12 k\$Most likely= 25 k\$Maximum= 50 k\$Mean= 29 k\$P * <impact> = 6 k\$</impact> | Schedule Impact:        | PDF= 3-point - triangularMinimum= 1 monthsMost likely= 2 monthsMaximum= 3 monthsMean= 2 monthsP* <impact>= 0.4 months</impact> |

| Basis of<br>Estimate: | New firmware requires 1-3 months of rework, with a firmware                                                         | e engineer at 0.1-0.5   | FIE.                                                                                                                           |

| Cause or<br>Trigger:  |                                                                                                                     | Impacted<br>Activities: | Prototype and production firmware releases                                                                                     |

| Start date:           | 1-Jul-2017                                                                                                          | End date:               | 1-Jan-2024                                                                                                                     |

| Risk<br>Mitigations:  |                                                                                                                     |                         |                                                                                                                                |

| Risk<br>Responses:    |                                                                                                                     |                         |                                                                                                                                |

| More details:         |                                                                                                                     |                         |                                                                                                                                |

### RT-402-6-06-D TD - Baseline FPGA does not satisfy requirements (DOE)

| Risk Rank:            | 2 (Medium) Scores: Probability : 2 (L) ; Cost: 2 (M)<br>Schedule: 2 (M))                                                | Risk Status:                | Open                                                                                                                              |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Summary:              | Computation requirements of calorimeter trigger and corr                                                                | elator are not satisfied by | y the baseline FPGA.                                                                                                              |

| Risk Type:            | Threat                                                                                                                  | Owner:                      | Jeffrey W Berryhill                                                                                                               |

| WBS:                  | 402.6 TD - Trigger and DAQ                                                                                              | Risk Area:                  | Technical Risk / Reliability or<br>Performance                                                                                    |

| Probability<br>(P):   | 20%                                                                                                                     | Technical<br>Impact:        | 2 (M) - significantly substandard                                                                                                 |

| Cost Impact:          | PDF= 3-point - triangularMinimum= 126 k\$Most likely= 252 k\$Maximum= 504 k\$Mean= 294 k\$P * <impact>= 59 k\$</impact> | Schedule Impact:            | PDF= 3-point - triangularMinimum= 1 monthsMost likely= 3 monthsMaximum= 6 monthsMean= 3.33 monthsP* <impact>= 0.7 months</impact> |

| Basis of<br>Estimate: | 12.5/25/50% FPGA cost increase on (36+48=) 84 FPGAs a                                                                   | t 12k/chip base cost. 1/3   | 3/6 months delay for procurement.                                                                                                 |

| Cause or<br>Trigger:  |                                                                                                                         | Impacted<br>Activities:     |                                                                                                                                   |

| Start date:           | 1-Jan-2020                                                                                                              | End date:                   | 1-Jan-2024                                                                                                                        |

| Risk<br>Mitigations:  |                                                                                                                         |                             |                                                                                                                                   |

| Risk<br>Responses:    |                                                                                                                         |                             |                                                                                                                                   |

| More details:         |                                                                                                                         |                             |                                                                                                                                   |

# **Additional Risk Mitigation**

- R&D is well underway for some of the key technologies to be used (optical links at >10Gbps, Ultrascale FPGAs, large LUTs)

- Completion of the design and manufacture of the Advanced Processor prototype (APd1), and the demonstrator will validate the technology by end of 2019

- R&D program of realistic firmware to demonstrate that FPGA resource usage and latency are within specs by time of demonstrator

- The Advanced Processor is modular with mezzanines and RTMs for optical links, memory, control, etc.

- Limits risk impact during production

# Contributing Institutions and Resource Optimization

4/4/18 Wesley Smith HL-LHC CD-1 Director's Review

### **Contributing** Institute

- University of Wisconsin Madison

- CMS Regional Calorimeter Trigger

- Operated from 2007 2015

- 22 (18 + spare/test) 9U-crate 1800-card system based on 5 distinct custom (UW-designed) high-speed ASICs and including 28 highspeed 160 MHz backplanes, 154 Receiver Cards 154 Electron ID Cards, 25 Jet Summary Cards, 25 Clock Cards and a 1400 card 4 Gbit/s copper serial data link mezzanine card system with associated testing cards.

### CMS Stage 1 and Stage 2 Layer-1 Calorimeter Triggers

- 22 CTP7's including hot spares

- Stage-1 was main calorimeter trigger for 2015 integrated w/RCT

- Stage-2 operating in parallel since 2015 main cal. Trig. for 2016 onward.

- 26 CTP7's used in Phase 2 Trigger R&D Program (see Tech. Overview)

- Wesley Smith (U. Wisconsin) \_ Professor

- CMS Trigger Project Manager 1994 2007, CMS Trigger Coordinator, 2007 2012

- Co-chair, CMS Trigger Performance & Strategy Working Group, 2012 2015 (Trigger Chapter of CMS HL-LHC Technical Proposal)

- US CMS Trigger L2 Project Manager 1997 present,

- US CMS Phase 1 Trigger L2 Upgrade Project Manager, 2013-2017

- Sridhara Dasu (U. Wisconsin) Professor

- US CMS L3 Manager Calorimeter Trigger (construction & operations) 1998 present

- US CMS L3 Manager Phase 1 Calorimeter Trigger Upgrade 2013 2017

- Sascha Savin (U. Wisconsin) Senior Scientist

- 4 years of HL-LHC Trigger Studies, CMS Future Standard Model Physics Group Co-Convener.

- CMS Standard Model Physics Convener, Trigger Studies Group Trigger Performance Convener

- Tom Gorski (U. Wisconsin) Electrical Engineer

- Over a decade of engineering on the CMS Calorimeter Trigger

- Delivered final phase of original Regional CMS Calorimeter Trigger

- Delivered Phase 1 Layer-1 Calorimeter Trigger Upgrade Electronics

- Ales Svetek (U. Wisconsin) Firmware Engineer

- 4 yrs on Phase 1 Calorimeter Trigger Upgrade Firmware

- (4 yrs ATLAS Beam Conditions Monitor FW, DAQ, Commissioning, Det. Ops.)

- Marcelo Vicente (U. Wisconsin) Firmware Engineer

- 4 yrs on Phase 1 Calorimeter Trigger Upgrade Firmware + HCAL Firmware

- 2 yrs on ECAL Phase 1 Upgrade Trigger Primitive Generation Electronics

- Jes Tikalski (U. Wisconsin) Software Engineer

- 4 yrs on Phase 1 Calorimeter Trigger Upgrade Software and embedded systems

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/18

4/4/1

4/4/18

### University Resources

- U. Wisconsin has an experienced electronics engineering, technical, firmware and software team that has delivered two successful CMS calorimeter trigger electronics systems on schedule and on budget using U. Wisconsin Physics Dept. lab facilities for final assembly and testing.

- Provided additional systems for Phase 2 R&D effort

- Mutual support and task sharing through APx consortium members

- Fermilab, U. Florida, Notre Dame, U. I. Chicago, U. Virginia

### Vendor Resources

- The Wisconsin team works with experienced vendors regularly qualified through R&D, pre-production and production orders for board manufacture, parts ordering and board assembly.

- Only non-vendor assembly are final parts needing installation after initial testing (e.g. heat-sink, surface connection cables).

- Where possible, State of Wisconsin purchasing is leveraged with placement of major parts orders through State Contract Vendors, including AVNET (Xilinx partner).

- All ES&H aspects of the HL LHC CMS Detector Upgrade Project will be handled in accordance with the Fermilab Integrated Safety Management approach, and the rules and procedures laid out in the Fermilab ES&H Manual (FESHM)

- We are following our Integrated Safety Management Plan (<u>cms-doc-13395</u>) and have documented our hazards in the preliminary Hazard Awareness Report (<u>cms-doc-13394</u>)

- In General Safety is achieved through standard Lab/Institute practices

- No construction, accelerator operation, or exotic fabrication

- No imminent peril situations or unusual hazards

- Items comply with local safety standards in site of fabrication and operation

- Site Safety officers at Institutes identified in the SOW

- Specific Safety for this WBS

- Modules similar to others built before, of medium size and no high voltage

- Integrated into existing well-tested and long-term performing safety system

- All activities and personnel at CERN regulated by CERN Safety Rules

- e.g. safety training courses required of all personnel

# Quality Assurance and Quality Control

- QA/QC for hardware: follows cms-doc-13093

- QA: All boards are designed for manufacturability, evaluated through prototyping

- QC: Full testing at the institute before shipping to CERN.

- All tests are recorded (of all types) for individual boards in the database.

- The tests use and validate the software and firmware test releases.

- QC: After shipment and receipt at CERN there is acceptance testing in the individual testing labs in the Electronics Integration Center (EIC) at CERN, where the boards are retested to validate the institute test results. These tests use the same software and firmware test releases as used in the institute testing. (Trigger boards also have Built In Self Test usable at power-up)

### QA/QC for Firmware, Online and Offline Software

- Produced in a sequence of releases with specific functionality requirements for each release to be demonstrated with specific tests defined to validate each release.

- Requirements will include performance metrics by which the software and firmware can be verified to satisfy the system requirements.

- Specific testing procedures will be established to certify that the software emulation of the hardware meets requirements by specifying specific tests with specific input and output data files.

- The releases will comply with the Software Quality Assurance procedures of the Fermilab Software Quality Assurance Program specified in QAM 12003 and the Software Assurance Grading and Inventory Procedure specified in QAM 12090.

Charge #4

# Production and Design QA/QC

### Design

- Design reviews

- Engineering analysis

- Engineering demonstration (with prototypes)

- Production

- Qualification testing

- Inspection

- Partial construction of initial boards "pilot run"

- Thorough suite of tests at institute before shipment

- Tests duplicated when boards arrive at CERN

- Project costs for M&S and Labor based on Phase-1 experience, reinforced by R&D program.

- M&S Costs validated with quotes for major parts costs

- ES&H, QA/QC plans, C&S based on experience with Phase-1 Upgrade

- Management and Engineering teams are experienced with sufficient design skills, having designed and built original CMS trigger and Phase-1 upgrade.

- Firmware and software tasks based on Phase-1 models and experience.

- Firmware development will exploit new High Level Synthesis tools

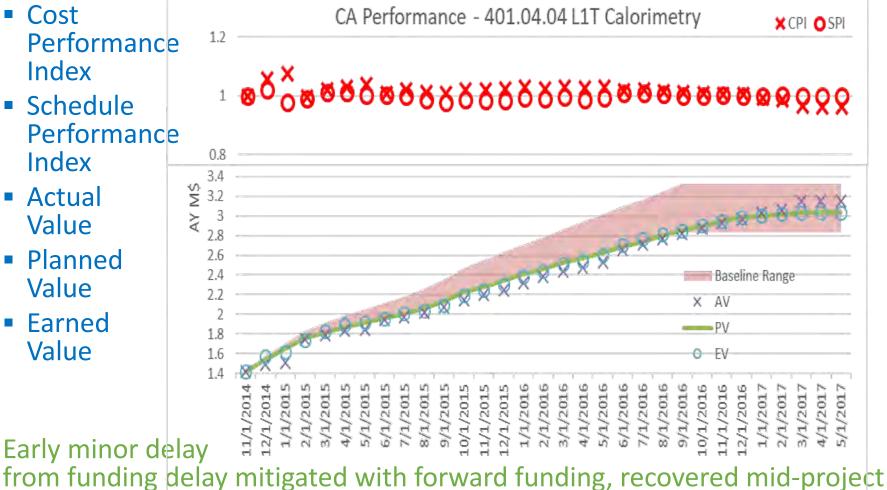

# **Phase-1 Project Performance**

- L1 Calorimeter Trigger Control Account History superb

- Excellent performance on:

- Actual

- Earned

4/4/18

- Subsystem interconnect test at the end of CY19:

- Prototypes used

- Calorimeter  $BE \rightarrow Calorimeter Trigger \rightarrow Correlator$

- AP Consortium boards have same link technologies so Calorimeter trigger cards can temporarily serve as substitutes for Calorimeter BE to decouple schedules.

- Correlator is identical board to Calorimeter Trigger.

- Test provides input for Trigger TDR

- System integration test Mid-CY22

- Production Pilot Boards used

- Calorimeter  $BE \rightarrow Calorimeter Trigger \rightarrow Correlator$

- Final Test before production starts

- Final Major System test before shipment to CERN.